Visible to Intel only — GUID: evh1630621350139

Ixiasoft

2.1. Programmed Input/Output Design Example

2.2. Programmed Input/Output Design Example Functional Description

2.3. Programmed Input/Output Design Example Simulation Testbench

2.4. Single Root I/O Virtualization (SR-IOV) Design Example

2.5. Single Root I/O Virtualization (SR-IOV) Design Example Functional Description

2.6. Single Root I/O Virtualization (SR-IOV) Design Example Simulation Testbench

Visible to Intel only — GUID: evh1630621350139

Ixiasoft

2.2. Programmed Input/Output Design Example Functional Description

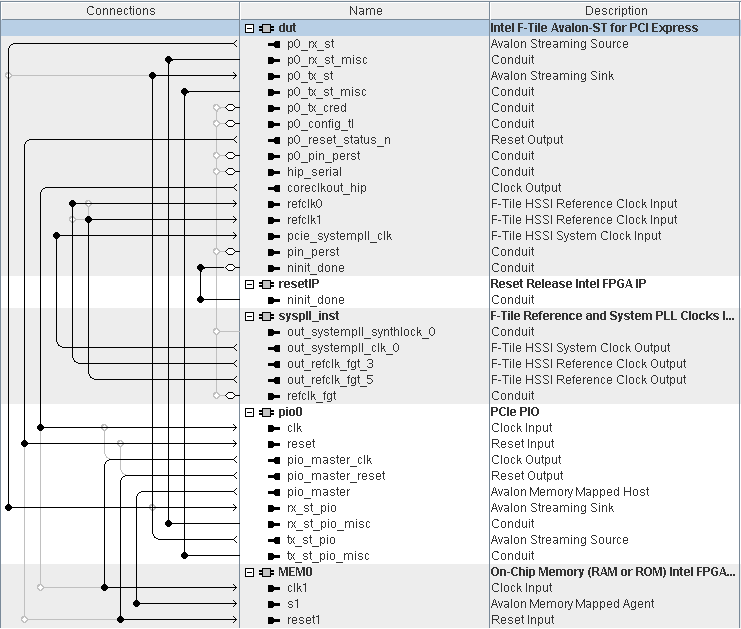

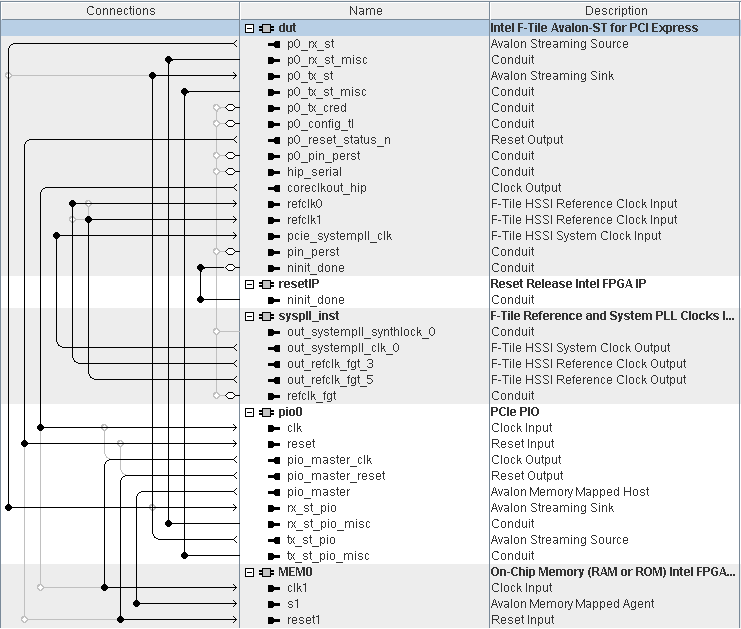

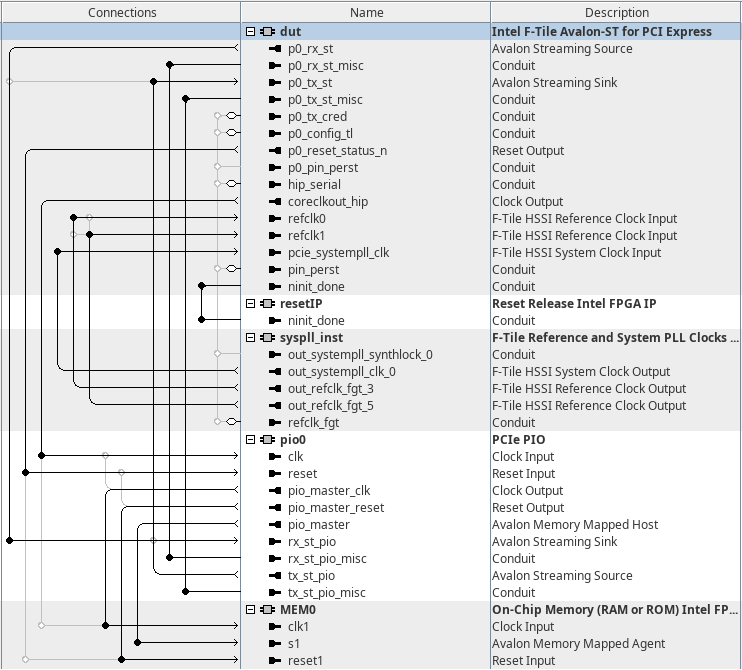

Figure 4. Platform Designer System Contents for F-Tile Avalon® -ST IP for PCI Express PIO Design Example [Gen4 x16 variant]The Platform Designer generates this design for up to Gen4 x16 variants.

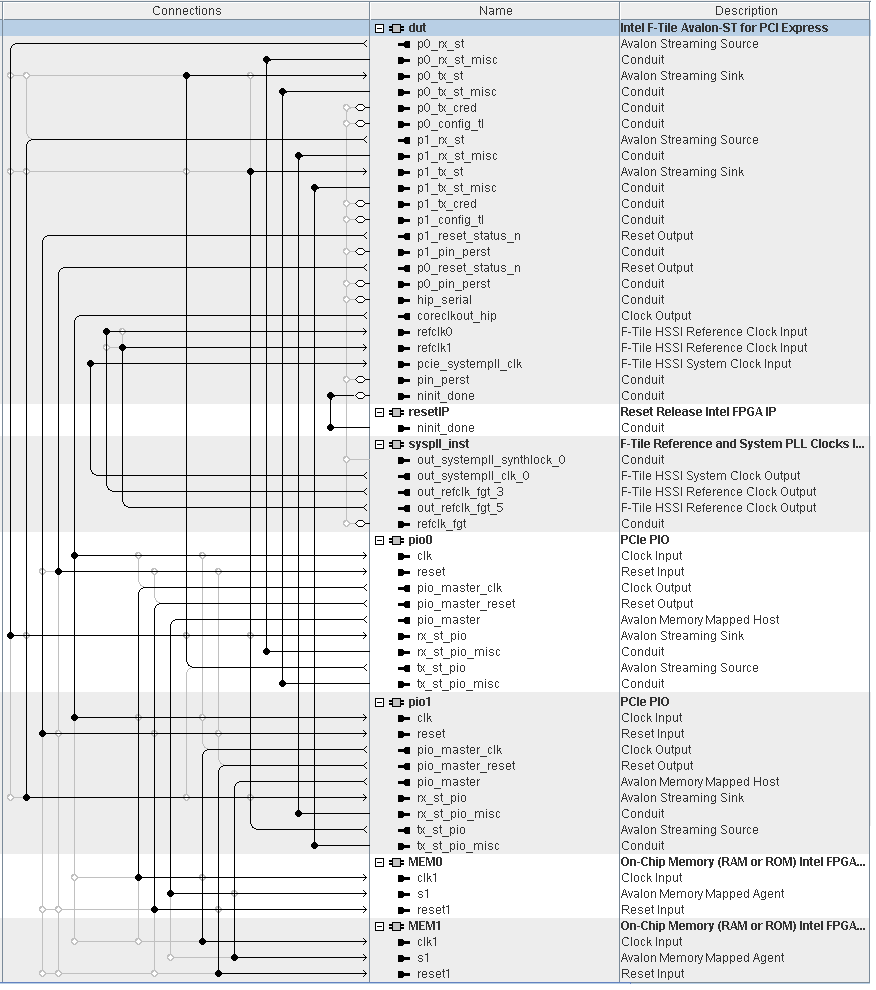

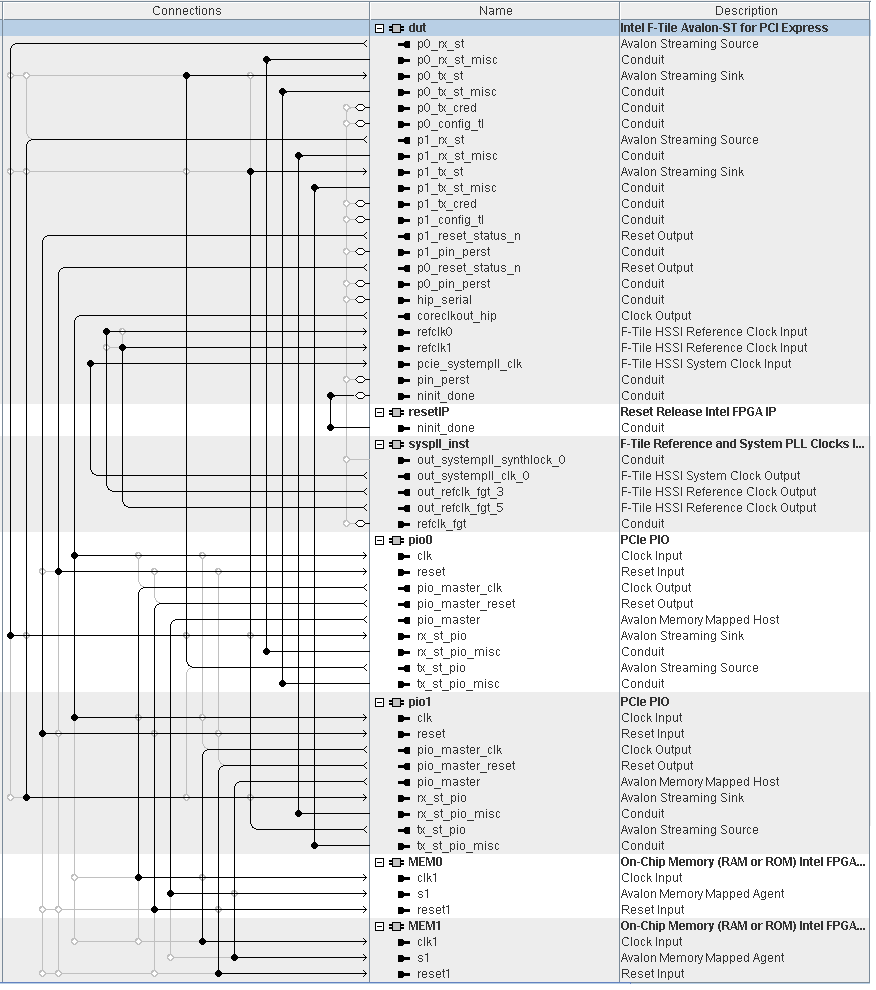

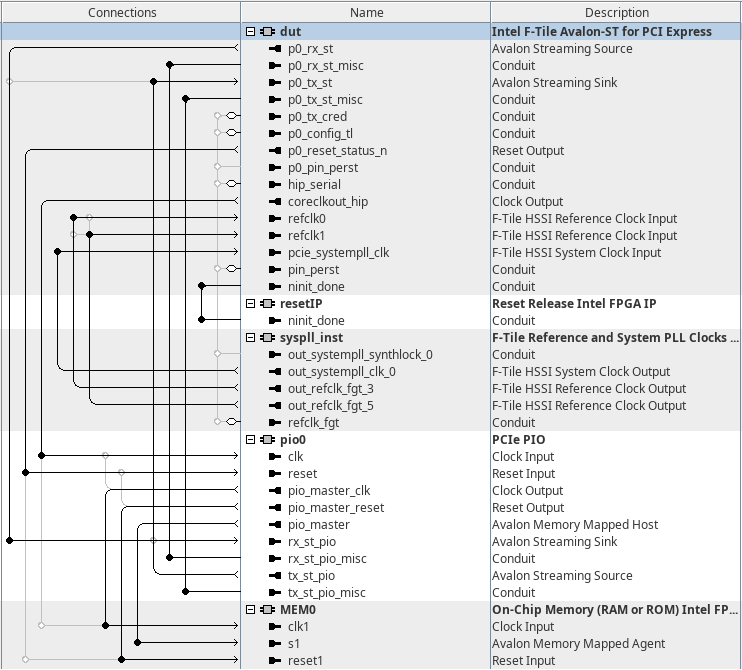

Figure 5. Platform Designer System Contents for F-Tile Avalon® -ST IP for PCI Express PIO Design Example [Gen4 x8x8 variant]

The Platform Designer generates this design for up to Gen4 x8x8 variants.

Figure 6. Platform Designer System Contents for F-Tile Avalon® -ST IP for PCI Express PIO Design Example [Gen4 x8 variant]

The Platform Designer generates this design for up to Gen4 x8 variants.

This design example includes the following components