Visible to Intel only — GUID: mwh1410383855277

Ixiasoft

Visible to Intel only — GUID: mwh1410383855277

Ixiasoft

2.6.8.5.2. End Multicycle Setup = 2 and End Multicycle Hold = 0

Multicycle Constraint

set_multicycle_path -from [get_clocks clk_src] -to [get_clocks clk_dst] \

-setup -end 2In this example, the setup relationship relaxes by a full clock period by moving the latch edge to the next latch edge. The hold analysis is does not change from the default settings. The following shows the setup timing diagram for the analysis that the Timing Analyzer performs. The latch edge is a clock cycle later than in the default single-cycle analysis.

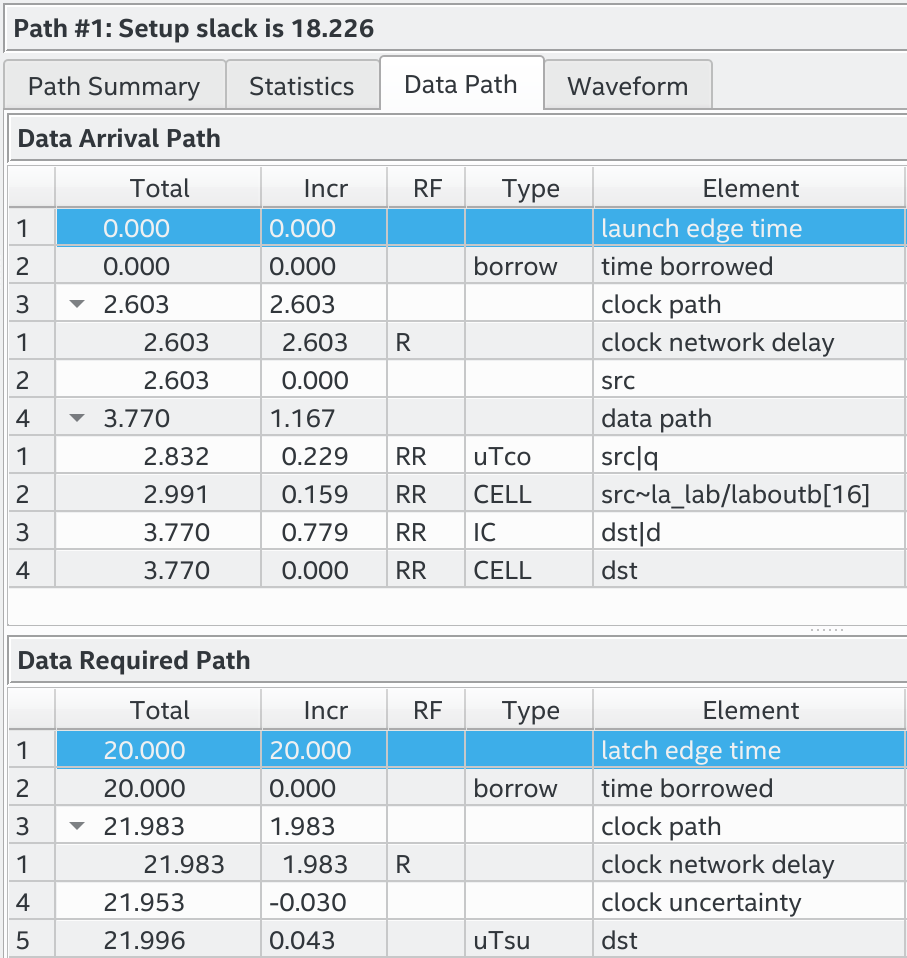

The most restrictive setup relationship with an end multicycle setup assignment of two is 20 ns. The following shows the setup report in the Timing Analyzer and highlights the launch and latch edges.

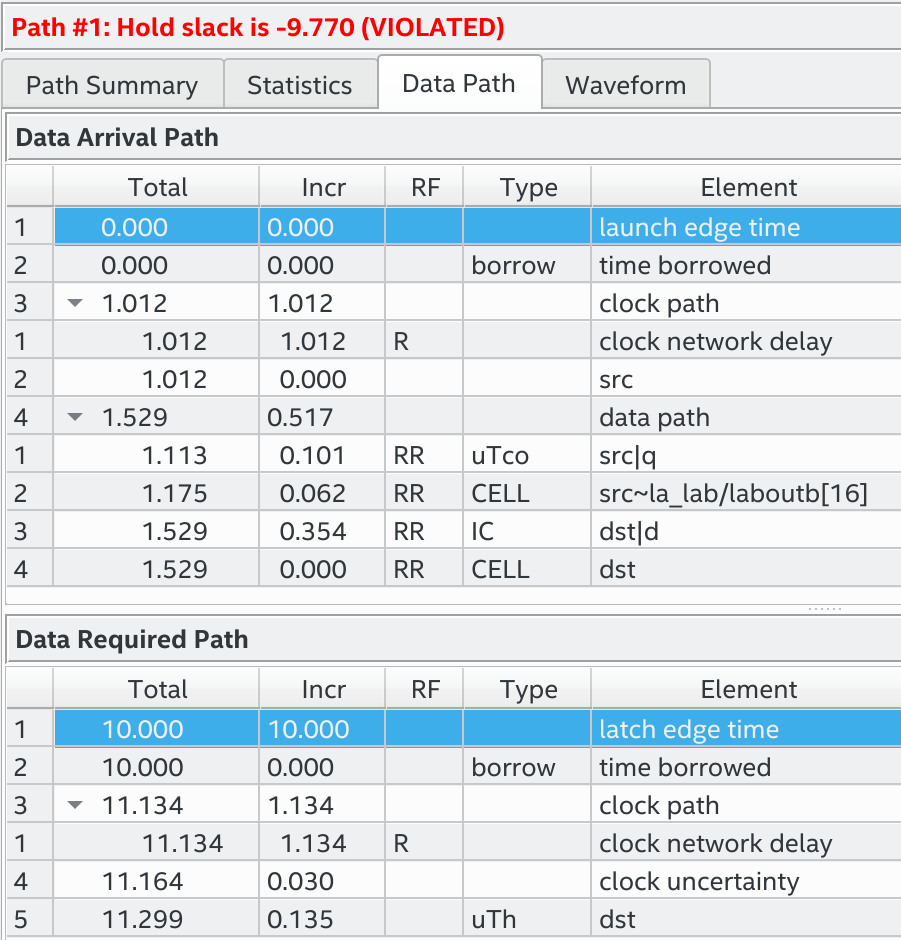

Because the multicycle hold latch and launch edges are the same as the results of hold analysis with the default settings, the multicycle hold analysis in this example is equivalent to the single-cycle hold analysis. The hold checks are relative to the setup check. Normally, the Timing Analyzer performs hold checks on every possible setup check, not only on the most restrictive setup check edges.