Visible to Intel only — GUID: mtr1430269516008

Ixiasoft

Visible to Intel only — GUID: mtr1430269516008

Ixiasoft

1.7.4.2. Fast Forward Details Report

Click any optimization Step in the report to view the implementation details and performance calculations for that step.

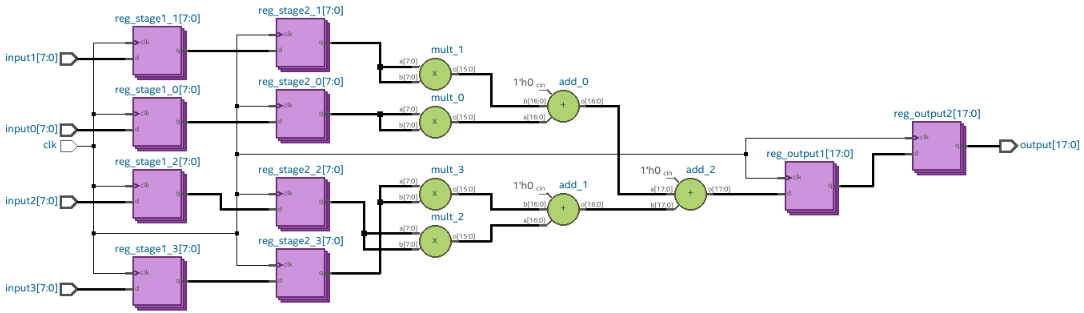

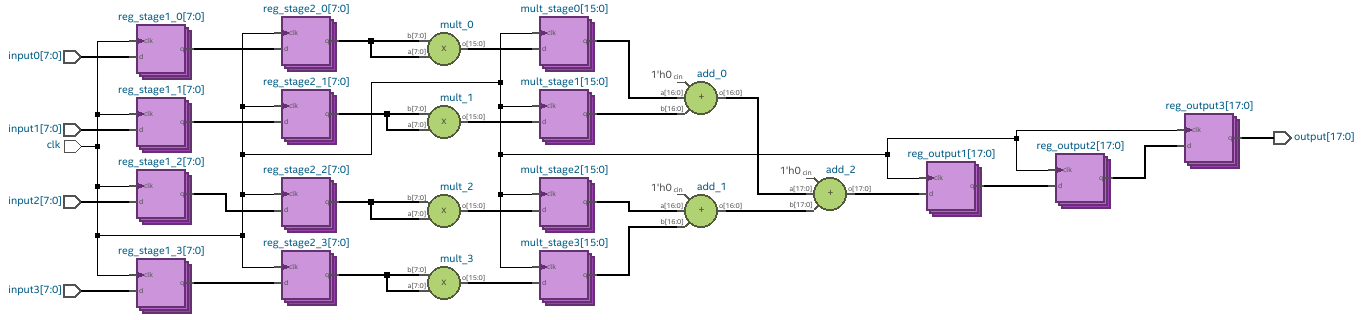

To illustrate the effectiveness of Fast Forward Timing Closure recommendations in enhancing the timing of your design, consider the following simple design composed of adders, multipliers, and registers:

Initially, this design is required to meet a maximum frequency of 800MHz. However, due to certain constraints, the maximum frequency is currently limited to 388.5MHz.

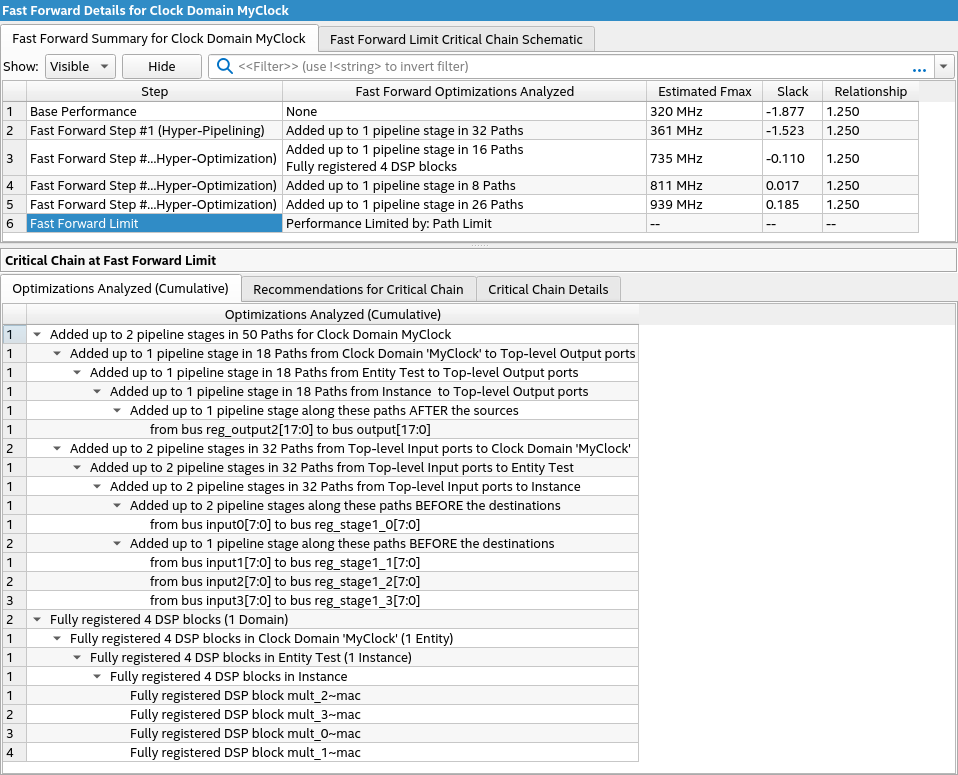

Upon executing the Fast Forward Timing Closure recommendations, proceed to review the Fast Forward Details Report. Within this report, you can find a breakdown of the optimization steps aimed at improving timing, as shown in the following image:

The Optimizations Analyzed tab shows two primary recommendations: adding pipeline stages in 50 paths and fully registering four DSP blocks. View the Recommendations for Critical Chain tab for specific guidance on implementing these optimizations at the RTL level.

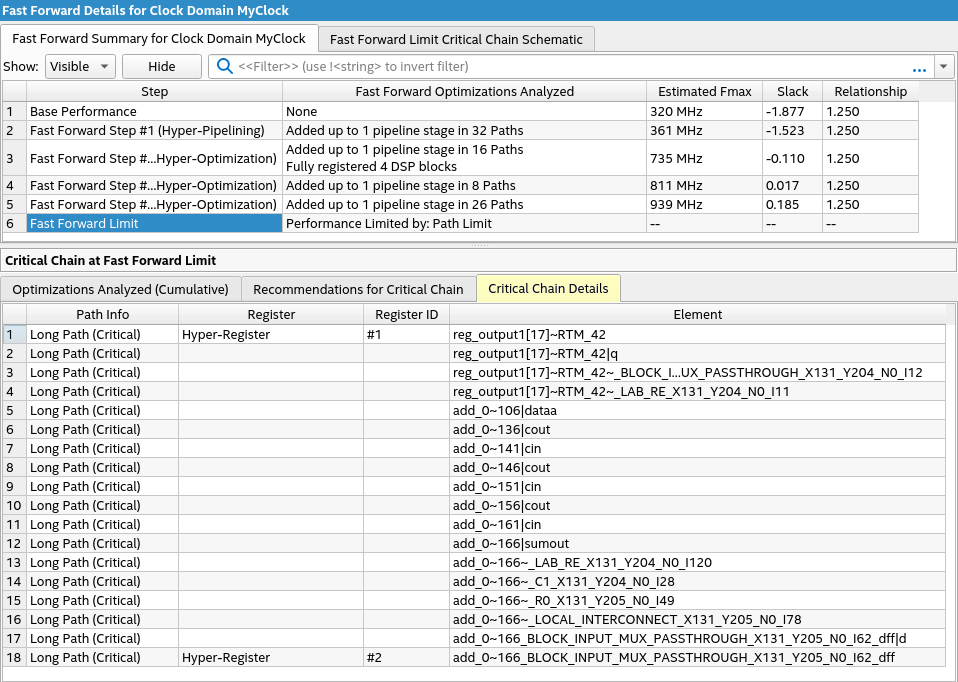

Additionally, explore the Critical Chain Details tab for a comprehensive description of the elements constituting the critical chain.

Refer to the following table for further details on each field:

| Report Field | Description |

|---|---|

| Step | Displays the pre-optimized Base Performance fMAX, the recommended Fast Forward optimization steps, and the Fast Forward Limit critical path that prevents further optimization. |

| Fast Forward Optimizations Analyzed | Summarizes the optimizations necessary to implement each optimization step. |

| Estimated Fmax | Specifies the potential fMAX performance if you implement all Fast Forward optimization steps. |

| Optimizations Analyzed For Fast Forward Step | Lists design recommendations hierarchically for the selected Step. Click the text to expand the report and view the clock domain, the affected module, and the bus and bits that require modification. |

| Optimizations Analyzed (Cumulative) | Accumulated list of all design changes necessary to reach the selected Step. |

| Critical Chain at Fast Forward Limit | Displays information about any path that continues to limit Hyper-Retiming even after application of all Fast Forward steps. The critical chain is any path that limits further Hyper-Retiming. Click the Fast Forward Limit step to display this field. |

| Recommendations for Critical Chain | Lists register timing path associated with the retiming limitations. Right-click any path to Locate Critical Chain in Fast Forward Viewer. |

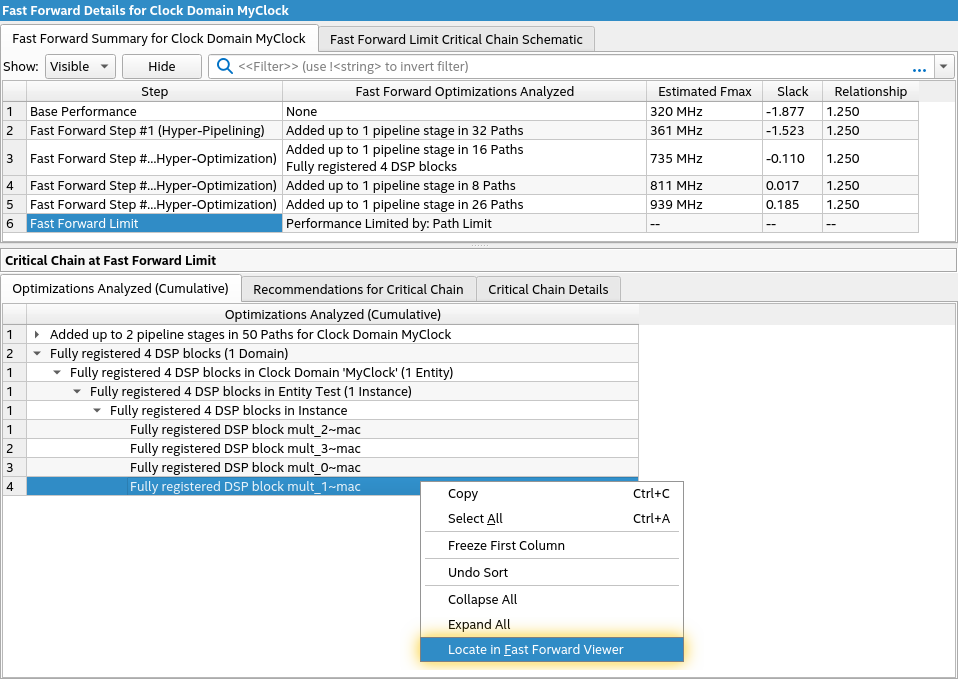

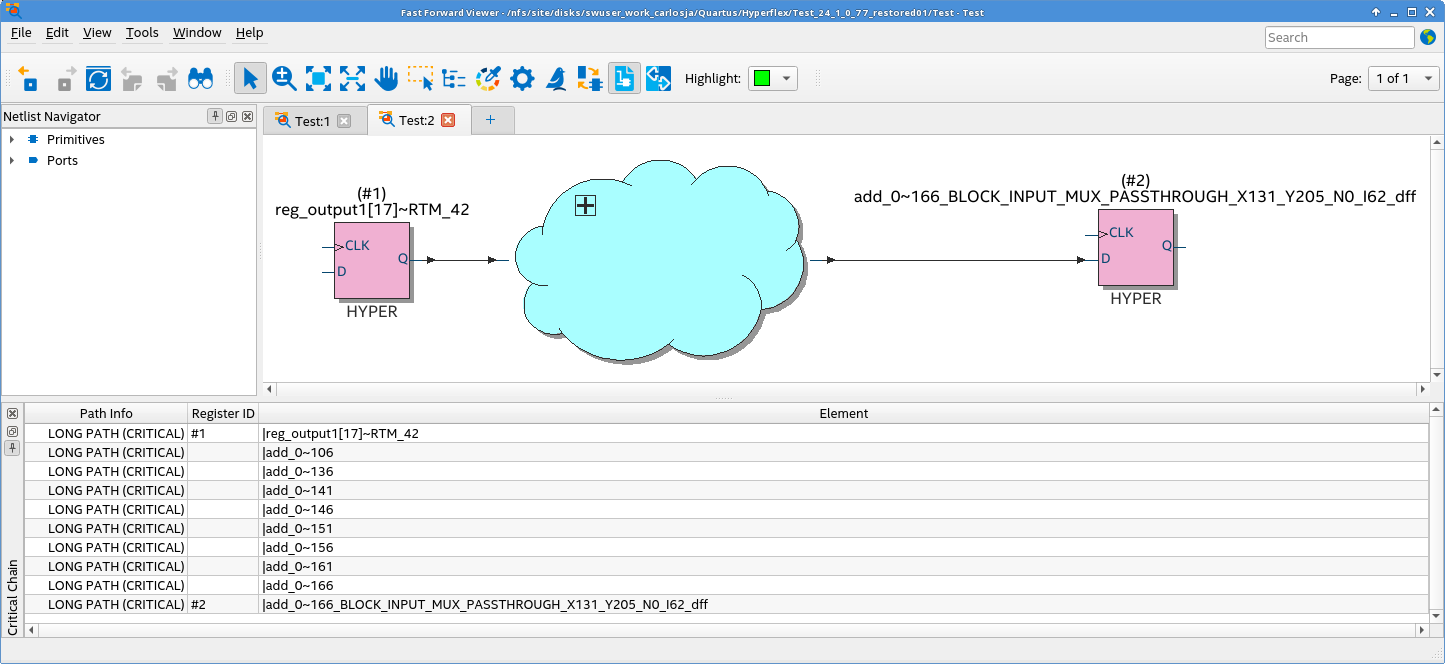

For a deeper analysis of the critical chains' structure, utilize the Fast Forward Viewer's cross-probing feature, as shown in the following image:

Based on the recommendations of the Fast Forward Details report, for this example, implement additional registers in the DSP blocks and an additional pipeline stage between reg_output_2 and output. When you implement these modifications, the updated design takes the following form:

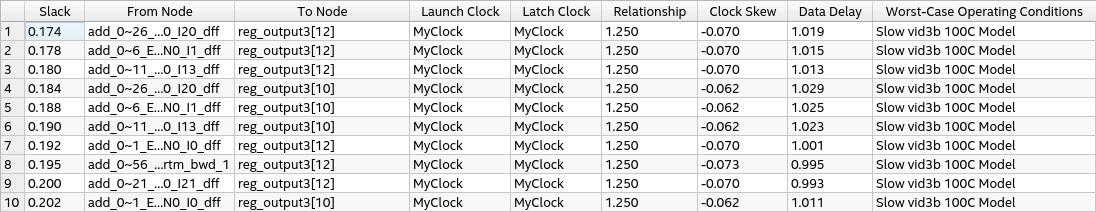

By repeating the compilation process and conducting a thorough analysis using the Timing Analyzer, you can observe tangible improvements in the timing performance of your designs.

Although some of the Fast Forward Timing Closure recommendations may present challenges in practical implementation within complex designs, they nonetheless offer valuable insights and opportunities for analysis. These recommendations serve as a valuable addition to your design optimization, providing a fresh perspective and uncovering potential ways for enhancing timing performance.