Visible to Intel only — GUID: ocl1513363708013

Ixiasoft

Visible to Intel only — GUID: ocl1513363708013

Ixiasoft

6.3.1. AXI Write Transaction

AXI Write Address

You can initiate an AXI write transaction by issuing a valid Write Address signal on the AXI Write Address Bus, AWADDR. The user logic should provide a valid write address in the AWADDR bus and assert the AWVALID to indicate that the address is valid. The master can assert the AWVALID signal only when it drives valid address and control information.

When the HBM2 controller is ready to accept a Write command transaction, it asserts the AWREADY signal. Address transfer happens when both AWVALID and AWREADY are asserted.

AWUSER, the user signal for auto precharge, also follows the same timing as AWADDR ; that is, AWUSER must be presented with the same timing of AWADDR.

AXI Write Data

During a write burst, the master asserts the WVALID signal only when it drives valid write data. Once asserted, WVALID must remain asserted until the rising clock edge after the slave asserts WREADY. The master must assert the WLAST signal while it is driving the final write transfer in the burst. User logic must issue the write data in the same order in which the write addresses are issued. Write data transfer happens when both WVALID and WREADY are HIGH.

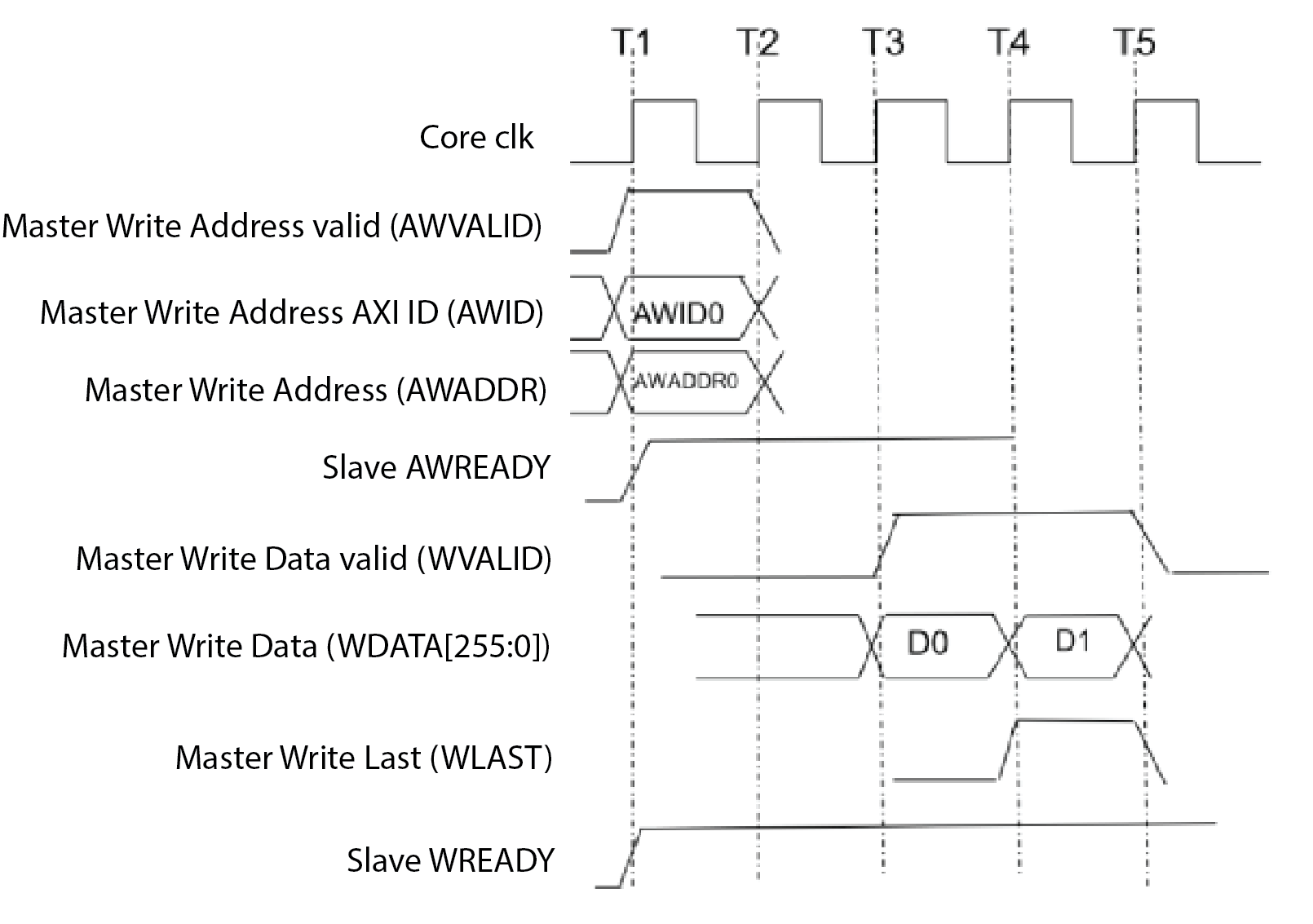

The following diagram illustrates a BL8 Write transaction. The master asserts the Write address (WA0) in T1 using transaction ID AWID0, the HBM2 controller asserts the AWREADY when it is ready to accept write requests. The master asserts the Write data in clock cycle T3. Because the controller WREADY is already asserted, the write data is accepted starting cycle T3. The last piece of the burst 8 transaction is asserted in clock cycle T4.

Write Response Channel

The HBM2 controller uses the Write Response channel to respond on successful Write transactions. The slave can assert the BVALID signal only when it drives a valid write response. When asserted, BVALID must remain asserted until the rising clock edge after the master asserts BREADY. The default state of BREADY can be high, but only if the master can always accept a write response in a single cycle.