Visible to Intel only — GUID: jba1434040209938

Ixiasoft

Visible to Intel only — GUID: jba1434040209938

Ixiasoft

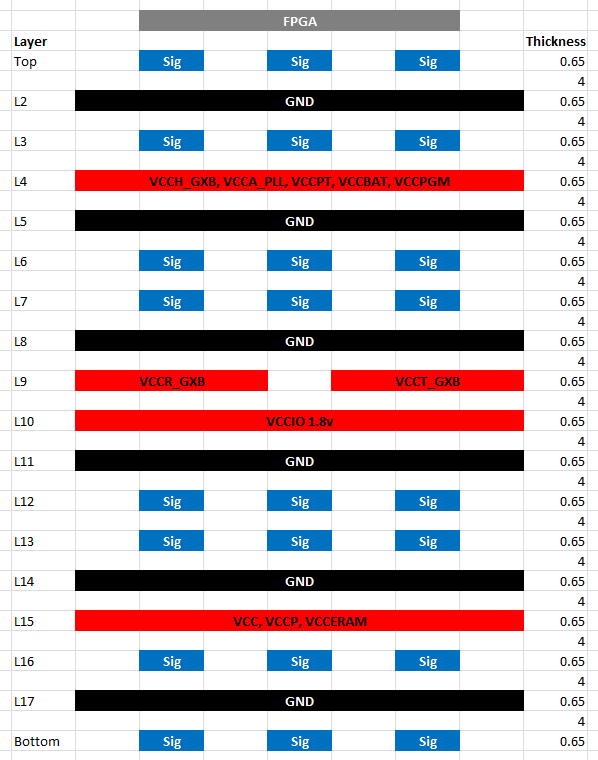

1.6.1. Initial Stackup Entry

The initial layer-stack of this design study is shown below.

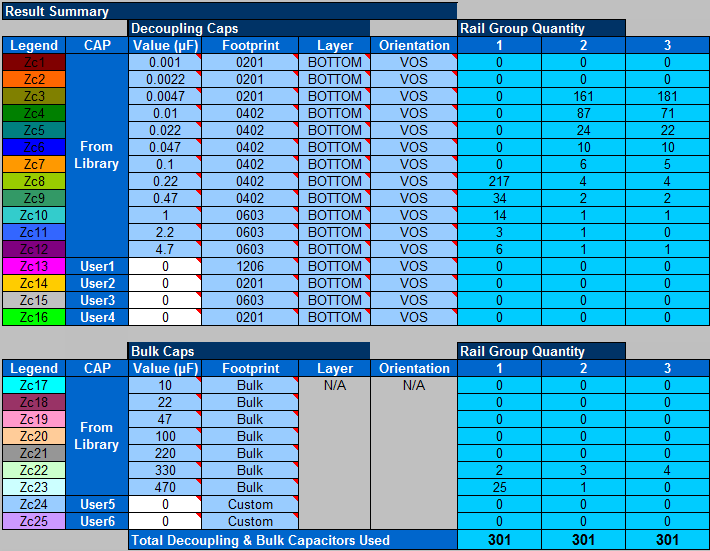

When entered into the PDN Tool, and Auto decoupling mode is selected for all power groups, it reports 301 capacitors are required to decouple each of the VCC, VCCT_GXB and VCCR_GXB supplies. When the PDN Tool decoupling mode is set to Auto, it will not add more than 301 capacitors. In reality, more than 301 capacitors will be required to decouple the design. Fitting in excess of 903 capacitors for three supplies is unrealistic so optimization of the PCB PDN is required.

Auto decoupling mode is used throughout this application note.

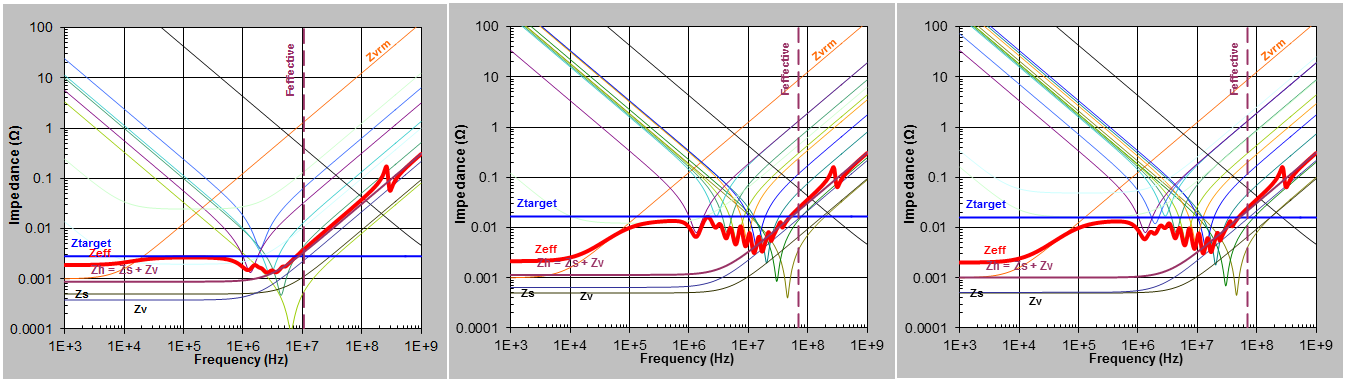

The following figure shows the impedance plots for VCC, VCCT_GXB and VCCR_GXB with this initial stackup and PDN Tool configuration.

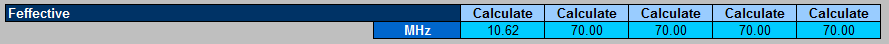

With this initial stackup and PDN Tool configuration, Feffective for the VCC supply is reported to be just 10.62MHz and the target Feffective of 70MHz for VCCT_GXB and VCCR_GXB supplies are not met. This is because the initial stackup, layer allocation, and PDN is not optimized, resulting in an inefficient PDN.