Visible to Intel only — GUID: djn1636763467736

Ixiasoft

Visible to Intel only — GUID: djn1636763467736

Ixiasoft

8.2.4.4. Eye Viewer

The F-Tile Debug Toolkit supports the Eye Viewer tool that allows you to measure the eye height margin for each channel. The Eye Viewer tool performs the eye measurement at BER = 1e-12, 95% confidence level or BER = 1e-9, 90% confidence level.

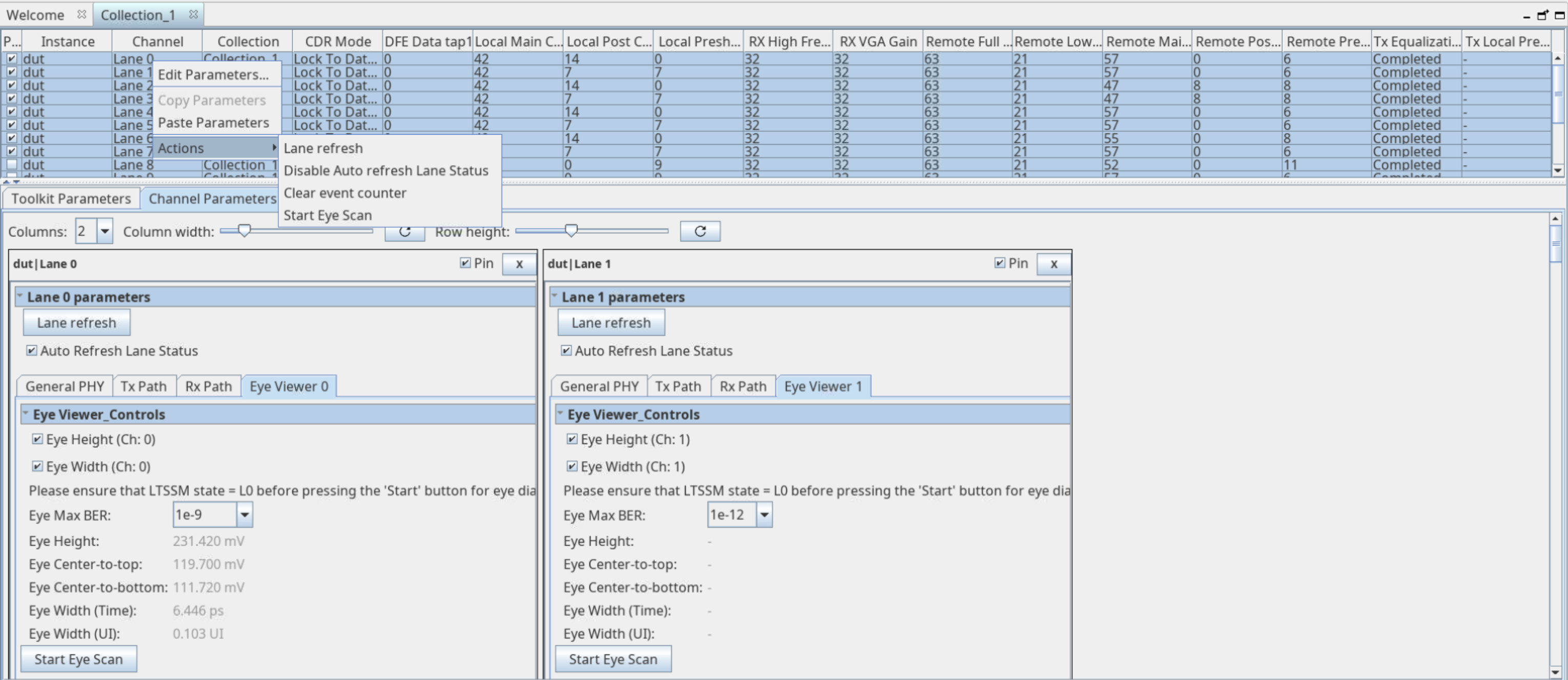

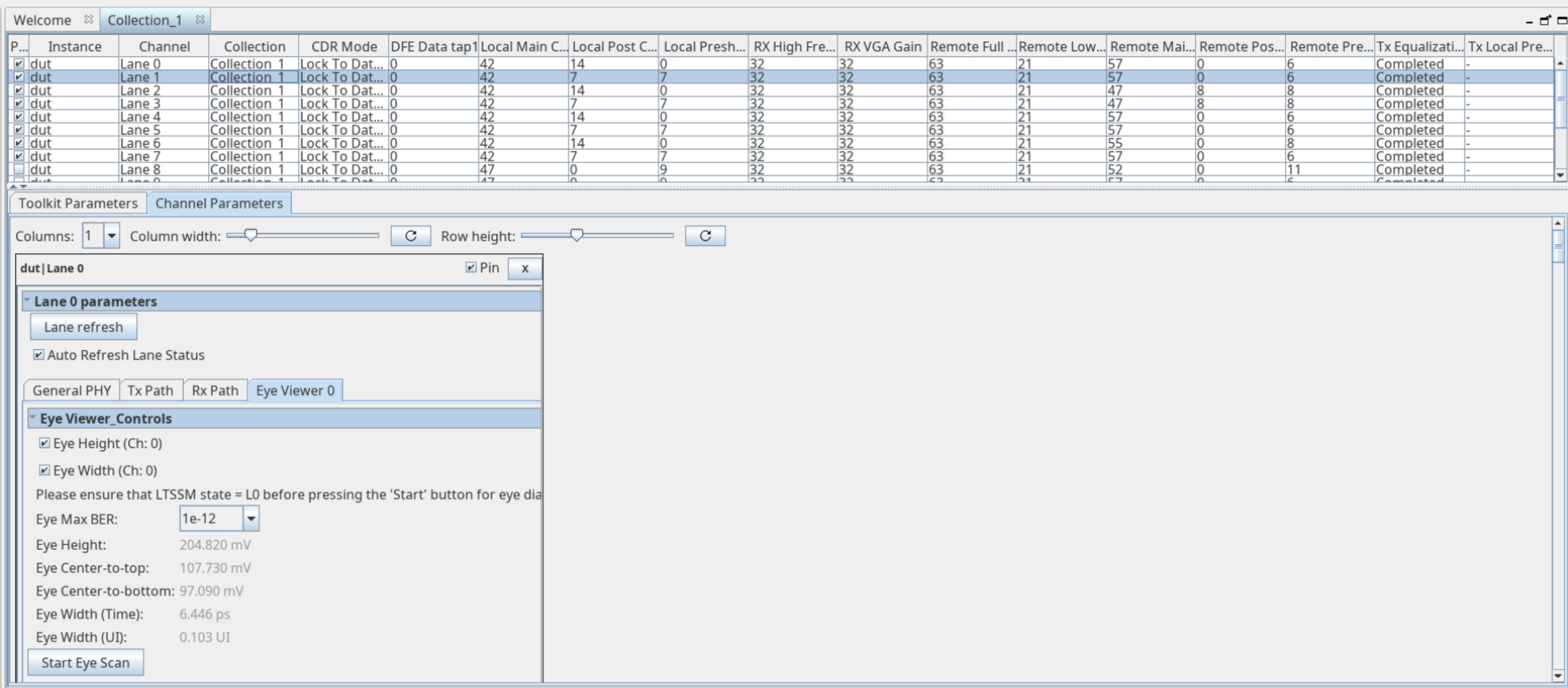

- To run Eye Viewer for a lane, select the lane from the Collection table.

- Select the Eye Viewer tab in the channel parameter window of the lane.

- Select Eye Height, Eye Width or both options and Eye Max BER.

- Click Start Eye Scan to begin the eye measurement for the selected lane.

- The messages window displays information messages to indicate the eye view tool's progress.

- Once the eye measurement completes, the eye height results are displayed.

To reduce the repetitive steps to run the Eye Viewer for more than one lanes, select the lanes from the Collection table, right click and select Start Eye Scan. The Eye Viewer runs for the selected lanes sequentially. Note that these steps are applicable for a BER of 1e-12 only.