Visible to Intel only — GUID: lro1429463779662

Ixiasoft

Visible to Intel only — GUID: lro1429463779662

Ixiasoft

1.3.1. Flash Programmer Target Design

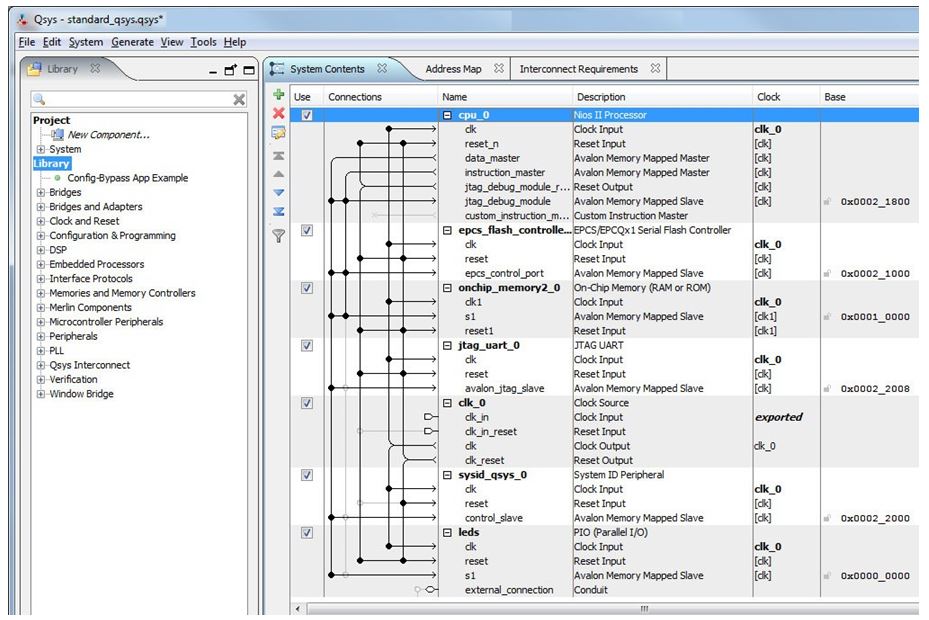

To use the Nios® II Flash Programmer, you must have a valid flash programmer target design downloaded to your board. A valid target design contains a Platform Designer system with at least the Platform Designer components shown in the "Minimum Component Set for the Flash Programmer Target Design" table.

The minimum component set provides facilities for the target design to communicate with the host and to write to flash memory. The minimum component set depends on the type of flash memory you intend to program. "Minimum Component Set for the Flash Programmer Target Design" lists the minimum component set for programming each kind of flash memory.

| Component | Flash Memory to Program | |||

|---|---|---|---|---|

| CFI | EPCS/EPCQx1 | EPCQ | On-Chip Flash ( Intel® MAX® 10) | |

| Nios® II processor, with JTAG debug module level1 or greater | Required | Required | Required | Required |

| System ID peripheral | Recommended | Recommended1 | Recommended1 | Optional |

| Generic Tri-State Controller | Required | |||

| Tristate Conduit Bridge | Required3 | |||

| Legacy EPCS/EPCQx1 Flash Controller | Required | |||

| Intel FPGA Generic Quad SPI Controller | Required 4 | |||

| Intel FPGA Generic Quad SPI Controller II | Required4 | |||

| Intel FPGA Serial Flash Controller | Required4 | |||

| Intel FPGA Serial Flash Controller II | Required4 | |||

| Intel On-Chip Flash | Required | |||

Hardware example designs capable of programming the flash memory are provided with development boards. If you are developing for a custom board, consider using one of these example designs as a starting point for your flash programmer target design.