Visible to Intel only — GUID: qat1707149864057

Ixiasoft

1. About the Performance Monitor (PMON) FPGA IP

2. Introduction to the Performance Monitor (PMON) IP

3. Performance Monitor IP Functional Description

4. Creating and Parameterizing the Performance Monitor (PMON) FPGA IP

5. Performance Monitor (PMON) FPGA IP Interface Signals

6. Document Revision History for the Performance Monitor (PMON) FPGA IP User Guide

A. Performance Monitor (PMON) Library Functions

Visible to Intel only — GUID: qat1707149864057

Ixiasoft

3. Performance Monitor IP Functional Description

The Performance Monitor (PMON) IP works as a pass-through bridge for an AXI4 connection between IPs. It accepts the AXI4 signals from a manager and sends commands to the AXI4 subordinate without modifying anything on the interface.

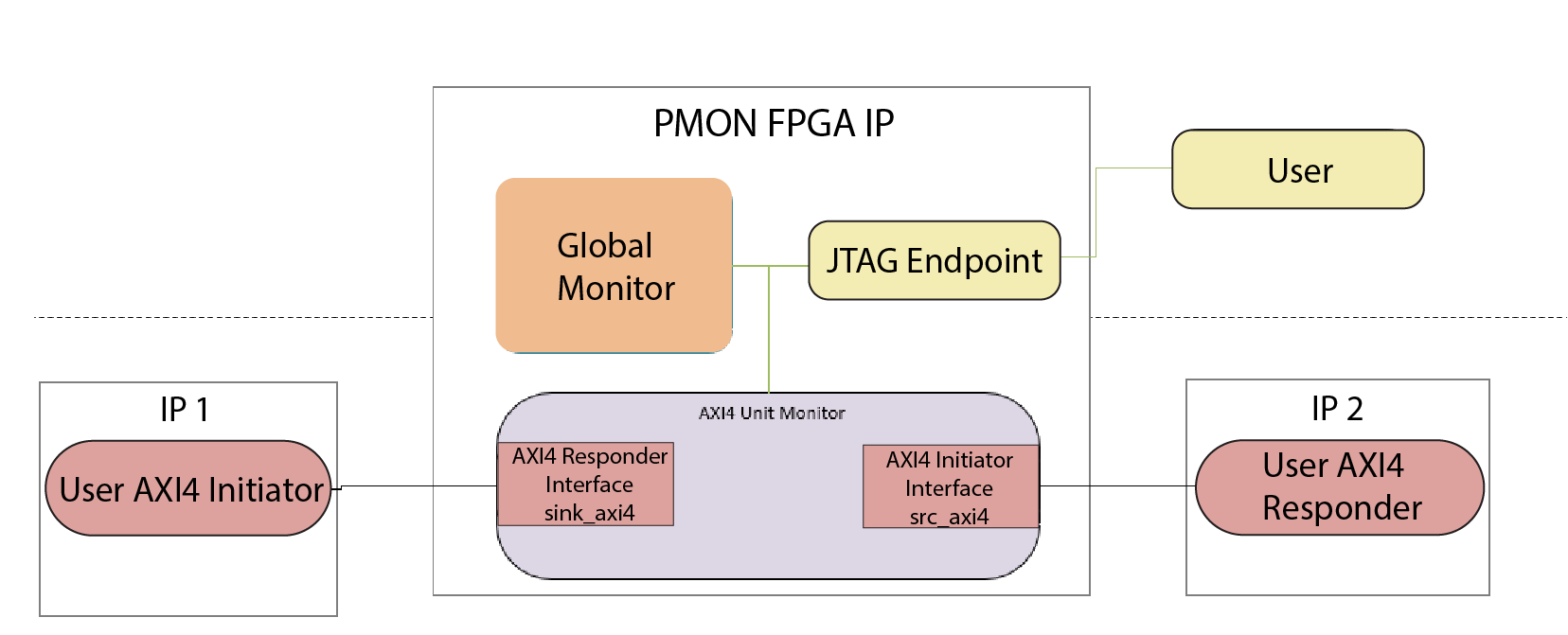

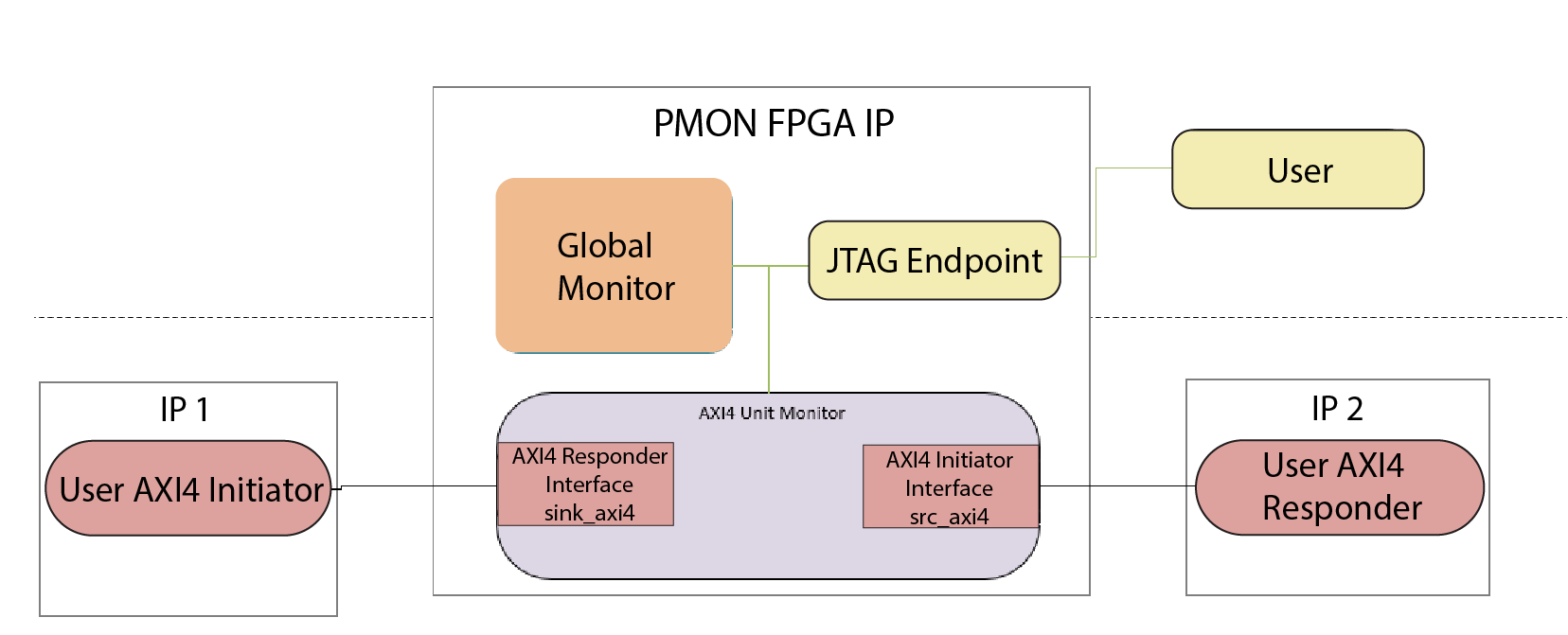

The following figure illustrates the PMON IP implementation.

Figure 1. PMON Implementation Block Diagram

The PMON IP instantiates two main blocks:

- AXI4 Unit Monitor. The unit monitor provides AXI4 sink and source interfaces through which traffic passes. The unit monitor does not interfere with or modify any signals on the interface; it simply monitors the interface and collects metrics based on the control status register (CSR) configuration.

- Global Monitor. The global monitor coordinates between multiple unit monitors in the system.

The User AXI4 Initiator acts as a manager and the AXI4 Responder functions as a subordinate.

Note:

- In the current release, the PMON IP supports only the AXI4 interface protocol.

- In the current release, the PMON IP supports only a one global to one unit monitor configuration.