Visible to Intel only — GUID: zmj1658414738584

Ixiasoft

1. About the High Bandwidth Memory (HBM2E) Interface FPGA IP Design Example User Guide

2. High Bandwidth Memory (HBM2E) Interface FPGA IP Design Example Quick Start Guide

3. High Bandwidth Memory (HBM2E) Interface FPGA IP Design Example Description

4. Document Revision History for High Bandwidth Memory (HBM2E) Interface FPGA IP Design Example User Guide

2.1. Creating an Quartus® Prime Project for Your HBM2E System

2.2. Configuring the High Bandwidth Memory (HBM2E) Interface FPGA IP

2.3. Generating the High Bandwidth Memory (HBM2E) Interface FPGA IP Design Example for Synthesis and Simulation

2.4. Compiling and Programming the Agilex™ 7 M-Series High Bandwidth Memory (HBM2E) Interface FPGA IP Design Example

2.5. Using the HBM2E Design Example with the Test Engine IP

2.6. Enabling and Using the HBM2E Design Example with the Performance Monitor

2.7. Using the AXI4-Lite-enabled HBM2E Design Example in Hardware and Simulation

2.8. Simulating the High Bandwidth Memory (HBM2E) Interface FPGA IP

2.8.1. High Bandwidth Memory (HBM2E) Interface FPGA IP Example Design For Simulation

2.8.2. Simulating High Bandwidth Memory (HBM2E) Interface FPGA IP with Synopsys VCS*

2.8.3. Simulating the HBM2E FPGA IP with ModelSim SE

2.8.4. Simulating the HBM2E FPGA IP with Cadence* Xcelium Parallel Simulator

2.8.5. Simulating High Bandwidth Memory (HBM2E) Interface IP Instantiated in Your Project

Visible to Intel only — GUID: zmj1658414738584

Ixiasoft

2.2. Configuring the High Bandwidth Memory (HBM2E) Interface FPGA IP

The following steps illustrate how to generate and configure the HBM2E FPGA IP. These steps illustrate the IP Catalog (standalone) configuration flow. The Platform Designer (standalone) flow is generally similar.

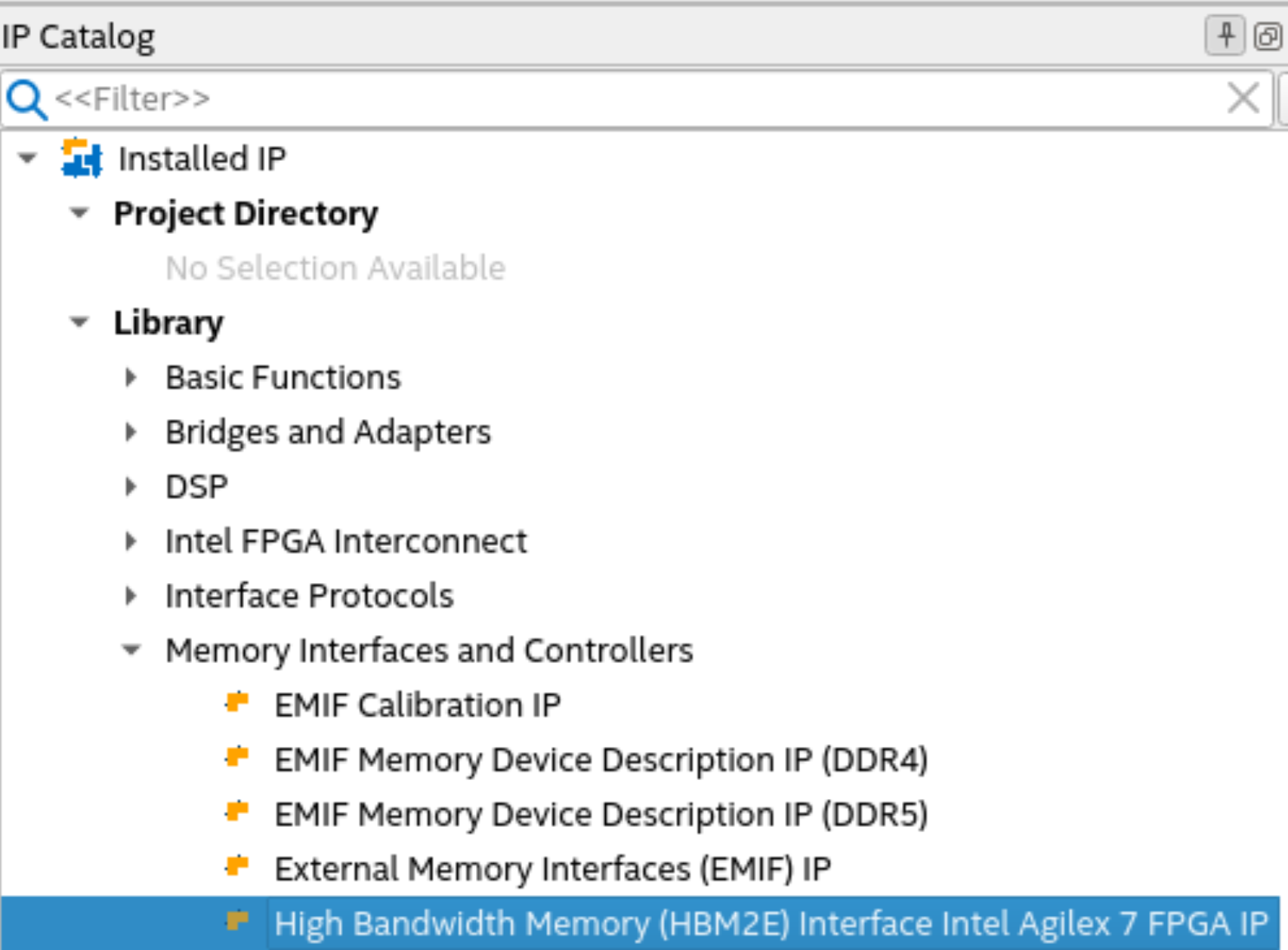

- Verify that the IP Catalog window is visible. If the IP Catalog window is not visible, select View > Utility Windows > IP Catalog.

- In the IP Catalog window, select Installed IP > Library > Memory Interfaces and Controllers > High Bandwidth Memory (HBM2E) Interface Agilex™ 7 FPGA IP.

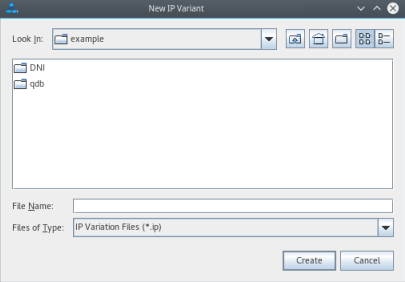

- In the New IP Variant window, type a name (<user instance name>) for your HBM2E IP in the File Name field. Click Create.

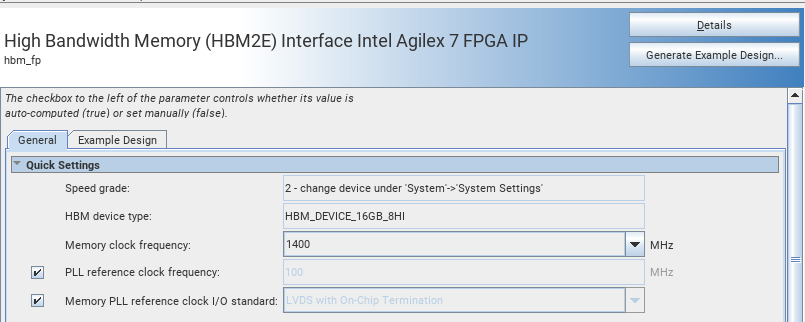

- In the IP Parameter Editor Pro window, configure the parameters on each tab to reflect actual HBM2E interface and system requirements. For information on individual parameters, refer to the Creating and Parameterizing the High Bandwidth Memory (HBM2E) Interface FPGA IP section in the High Bandwidth Memory (HBM2E) Interface Agilex™ 7 M-Series FPGA IP User Guide.