Visible to Intel only — GUID: cyl1667584519599

Ixiasoft

1. About the External Memory Interfaces Agilex™ 7 M-Series FPGA IP

2. Design Example Quick Start Guide for External Memory Interfaces Agilex™ 7 M-Series FPGA IP

3. Design Example Description for External Memory Interfaces Agilex™ 7 M-Series FPGA IP

4. Document Revision History for External Memory Interfaces Agilex™ 7 M-Series FPGA IP Design Example User Guide

2.1. Creating an EMIF Project

2.2. Generating and Configuring the EMIF IP

2.3. Configuring DQ Pin Swizzling

2.4. Generating the Synthesizable EMIF Design Example

2.5. Generating the EMIF Design Example for Simulation

2.6. Pin Placement for Agilex™ 7 M-Series EMIF IP

2.7. Compiling the Agilex™ 7 M-Series EMIF Design Example

2.8. Using the EMIF Design Example with the Test Engine IP

2.9. Generating the EMIF Design Example with the Performance Monitor

2.1.1.3.1. Generating a Custom Memory Preset File for DDR4

2.1.1.3.2. Guidelines for Selecting the DDR4 DRAM Component Package Type

2.1.1.3.3. Generating a Custom Memory Preset File for DDR5

2.1.1.3.4. Guidelines for Selecting the DDR5 DRAM Component Package Type

2.1.1.3.5. Generating a Custom Memory Preset File for LPDDR5

2.3.1. Example: DQ Pin Swizzling Within DQS group for x32 DDR4 interface

2.3.2. Example: Byte Swizzling for a x32 DDR4 interface, using a memory device of x8 width

2.3.3. Combining Pin and Byte Swizzling

2.3.4. Example: Swizzling for a x32 + ECC interface

2.3.5. Example: Swizzling for a 2Ch x32 + ECC interface

2.3.6. Example: Byte Swizzling for Lockstep Configuration

Visible to Intel only — GUID: cyl1667584519599

Ixiasoft

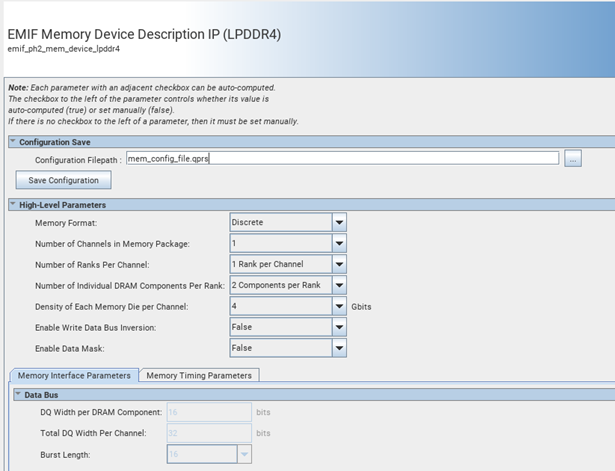

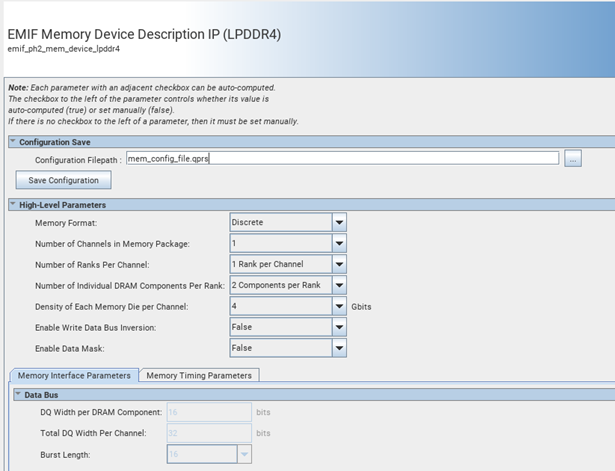

2.1.1.1. Memory Device Description IP Parameter Editor Guidelines

This topic provides high-level guidance for parameterizing the tabs in the Agilex™ 7 EMIF Memory Device Description IP parameter editor.

| Parameter Editor Tab | Guidelines |

|---|---|

| High Level Parameters | Ensure that you enter the following parameters correctly:

|

| Memory Interface Parameters | Select the required parameters for the following:

|

| Memory Timing Parameters | Allows you to modify the frequency and timing settings for the device. |

For detailed information on individual parameters, refer to the appropriate protocol-specific chapter in the External Memory Interfaces Agilex™ 7 M-Series FPGA IP User Guide.

Figure 6. EMIF Memory Device Description Parameter Editor