Visible to Intel only — GUID: xml1630477892657

Ixiasoft

1. About This Document

2. About the Nios® V Embedded Processor

3. Nios® V Processor Hardware System Design with Intel® Quartus® Prime Pro Edition and Platform Designer

4. Nios® V Processor Software System Design

5. Nios® V Processor Configuration and Booting Solutions

6. Nios® V Processor - Using the MicroC/TCP-IP Stack

7. Nios® V Processor Debugging, Verifying, and Simulating

8. Nios® V Embedded Processor Design Handbook Archives

9. Document Revision History for the Nios® V Embedded Processor Design Handbook

5.1. Introduction

5.2. Linking Applications

5.3. Nios® V Processor Booting Methods

5.4. Introduction to Nios® V Processor Booting Methods

5.5. Nios® V Processor Booting from Configuration QSPI Flash

5.6. Nios V Processor Booting from On-Chip Memory (OCRAM)

5.7. Summary of Nios V Processor Vector Configuration and BSP Settings

7.4.1. Prerequisites

7.4.2. Setting Up and Generating Your Simulation Environment in Platform Designer

7.4.3. Creating Nios V Processor Software

7.4.4. Generating Memory Initialization File

7.4.5. Generating System Simulation Files

7.4.6. Running Simulation in the QuestaSim Simulator Using Command Line

Visible to Intel only — GUID: xml1630477892657

Ixiasoft

2.3.3.1.1. Generating the Board Support Package using the BSP Editor GUI

Platform Designer includes the BSP Editor board support package editing tool. A board support package (BSP) provides a software runtime environment for embedded systems, such as Nios® V/m processor systems. The BSP Editor is a GUI tool that you can launch from Platform Designer to generate and configure BSP contents.

- In the Intel® Quartus® Prime software, go to Tools > Platform Designer .

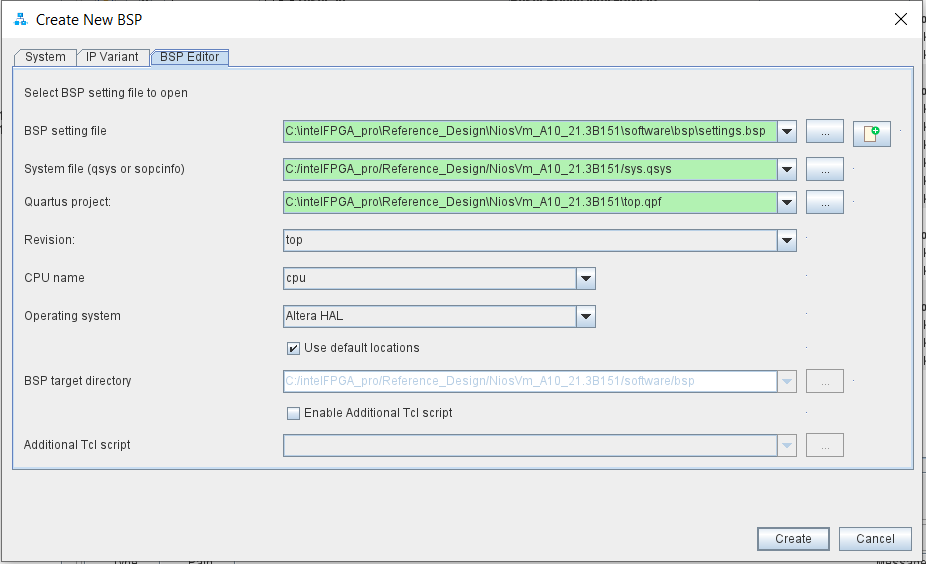

- In the Platform Designer window, go to File > New BSP. The Create New BSP window appears.

- For BSP setting file, create a BSP file (settings.bsp) in <Project directory>/software/bsp/settings.bsp.

- For System file (qsys or sopcinfo), select the Nios® V/m processor Platform Designer system (sys.qsys).

- For Quartus project, select the example design Quartus Project File (top.qpf).

- For Revision, select top.

- For CPU name, select cpu.

- Select the Operating system as Altera HAL or Micrium MicroC/OS II.

- Click Create to create the BSP file.

Figure 4. Create New BSP window

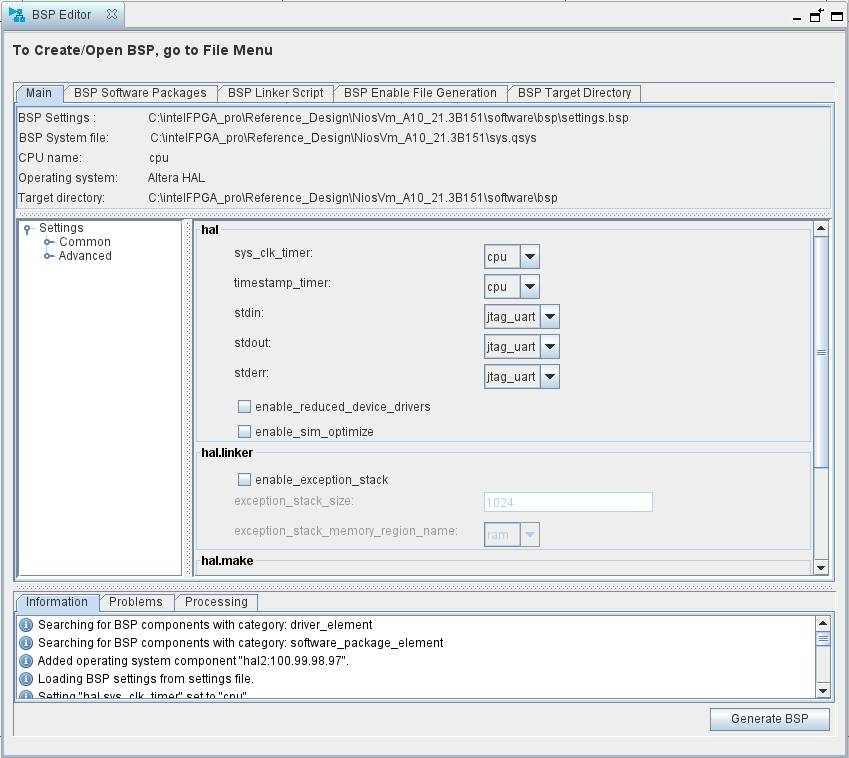

- Click Generate BSP to generate the BSP file.

Figure 5. BSP Editor

Note: In the BSP Editor, the default selection for sys_clk_timer and timestamp_timer are configured to cpu to use the Nios® V/m processor's internal timer.

Note: In the BSP Editor, the default selection for sys_clk_timer and timestamp_timer are configured to cpu to use the Nios® V/m processor's internal timer.

Related Information