Questa*-Intel® FPGA Edition Quick-Start: Intel® Quartus® Prime Pro Edition

ID

691278

Date

6/26/2022

Public

Visible to Intel only — GUID: mdv1626722584020

Ixiasoft

1.6. Compile and Simulate the Design

Run the top-level mentor_example.do script in the Questa*-Intel® FPGA Edition software to compile and simulate your design by performing the following steps:

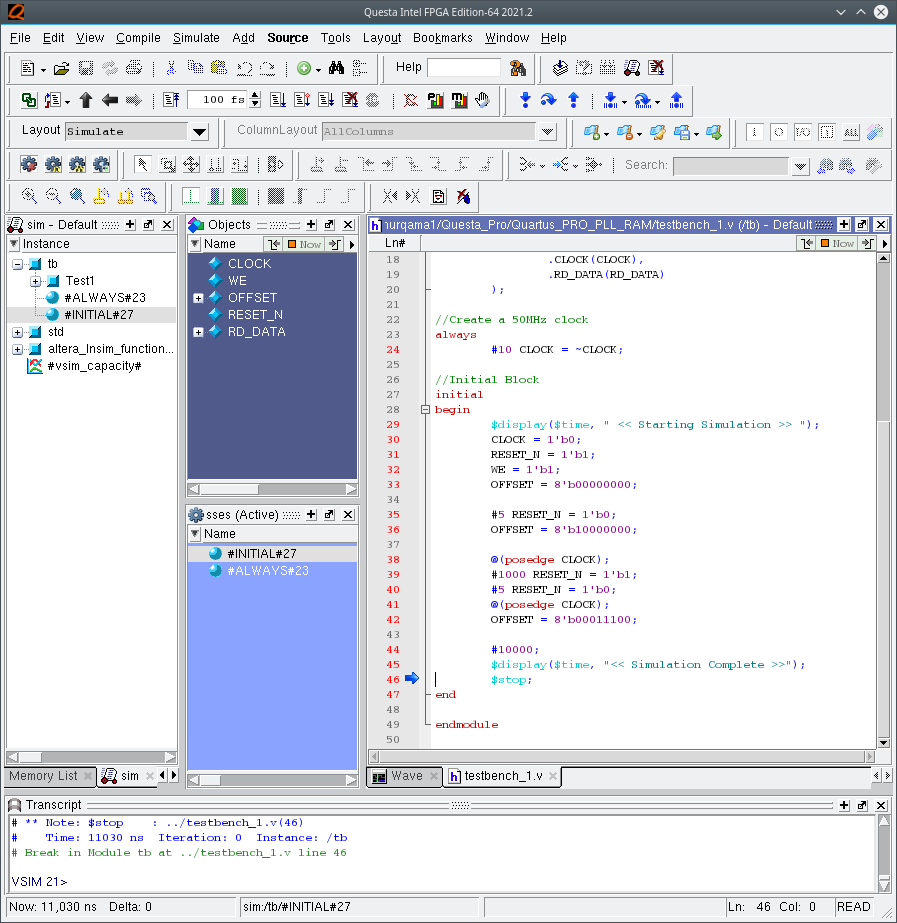

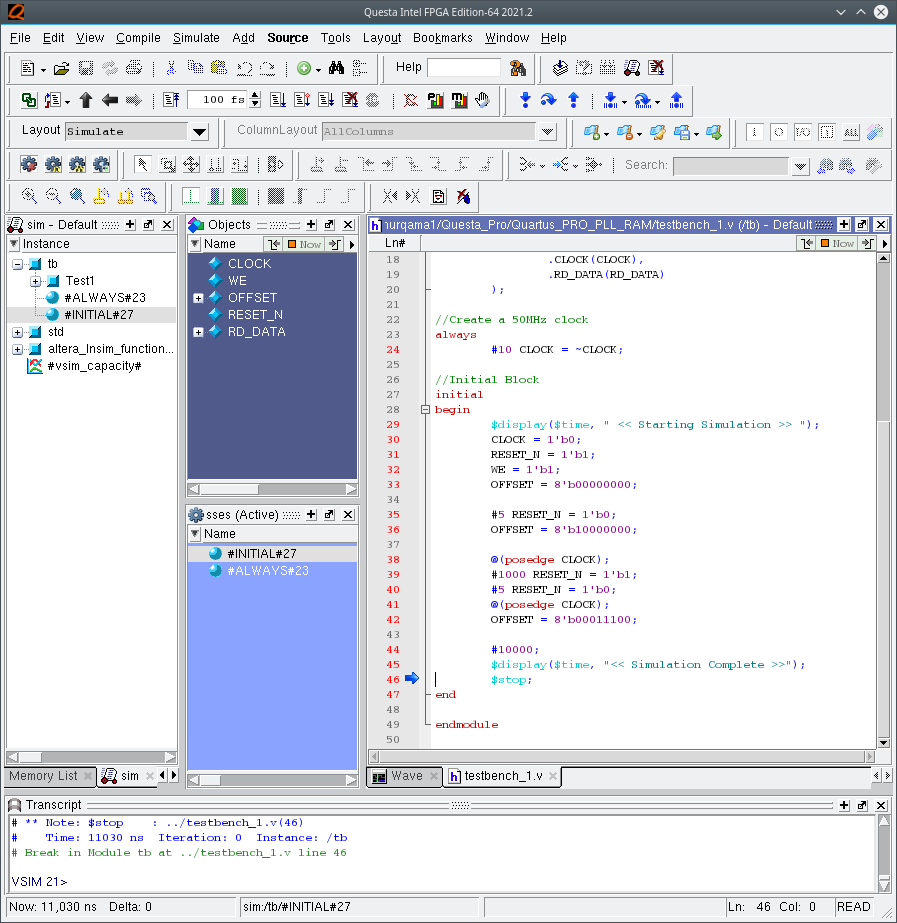

- Launch the Questa*-Intel® FPGA Edition software. The Questa*-Intel® FPGA Edition GUI organizes the elements of your simulation onto separate windows and tabs.

- From the PLL_RAM project directory, open testbench_1.v and mentor/mentor_example.do files.

- To display the Transcript window, click View > Transcript. Enter commands for Questa*-Intel® FPGA Edition directly in the Transcript window.

- Type the following command in the Transcript window and then press Enter:

do mentor_example.do

The design compiles and simulates according to your specifications in the mentor_example.do script. The following figure shows the Questa*-Intel® FPGA Edition simulator:

Figure 6. Questa*-Intel® FPGA Edition GUI