Visible to Intel only — GUID: kun1626722604508

Ixiasoft

1.8. Add Signals to the Simulation

The CLOCK, WE, OFFSET, RESET_N, and RD_DATA signals automatically appear in the Wave window because the top-level design defines these I/O. In addition, you can optionally add internal signals to the simulation.

Perform the following steps to add signals to the simulation:

- In the Objects window, locate the UP_module, DOWN_module, PLL_module, and RAM_module modules.

- In the Objects window, select RAM_module to view the module's inputs and outputs.

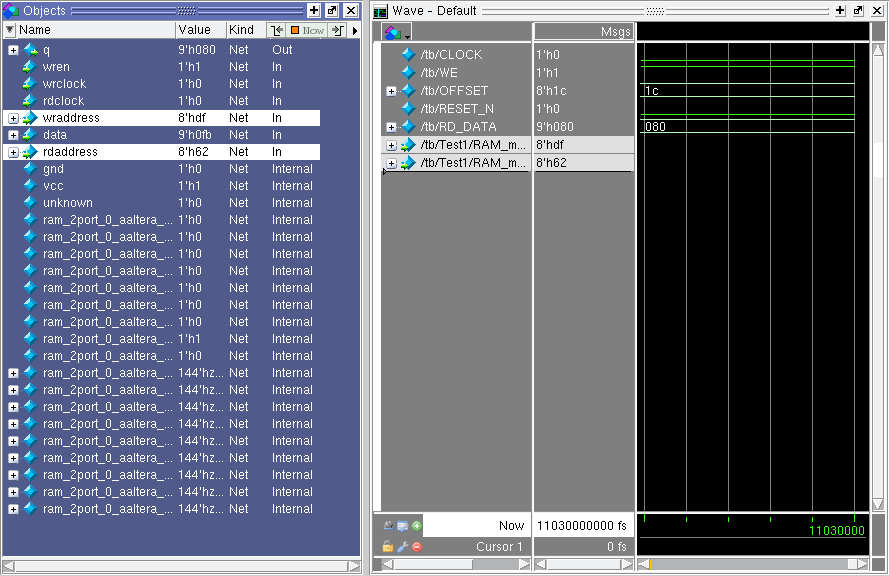

Figure 10. Add Signals to the Wave Window

- Right-click rdaddress and then click Add Wave to add the internal signals between the down-counter and dual-port RAM module.

- Right-click wraddress and then click Add Wave to add the internal signals between the up-counter and dual-port RAM module. Alternatively, you can drag and drop these signals from the Objects window to the Wave window.

- Click Simulate > Run > Continue to generate waveforms for the new signals you added.