Visible to Intel only — GUID: uaj1614207787953

Ixiasoft

Visible to Intel only — GUID: uaj1614207787953

Ixiasoft

3.6. Clocking

Word Clock

The word clock is a PMA parallel clock and equals the data rate divided by the PMA width. For example: 25.78125 Gbps data rate with 32-bit PMA width has a word clock of 25.78125 Gbps ÷ 32 = 805.6640625 MHz.

Bond Clock

The bond clock and the word clock are always PMA parallel clocks, and they are usually the same. However, in certain multi-lane (that is, more than one PMA) bonded configurations, the bond clock from every core interface comes from one primary PMA, while the word clock comes from the PMA associated with that core interface. Refer to Recommended Connection and Source for connection recommendations.

User Clock 1

User clock 1 is the divided version of the PMA data rate. The available division factor for user clock 1 depends on the PMA type.

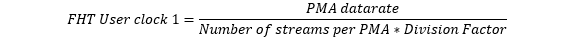

FHT: The user clock 1 for FHT is calculated as the PMA data rate divided by (number of streams * division factor).

You can specify a division factor using FHT user clk div33_34 select and FHT TX/RX user clk1 select. Division factors for FHT can be 33, 34, 66, 68, or 40.

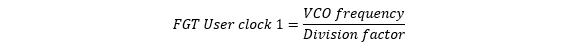

FGT: The user clock 1 for FGT is calculated as the VCO frequency divided by a division factor, which you specify in the TX/RX user clock div by parameter in the TX/RX User clock settings in the parameter editor.

The valid range of division factors FGT is from 12 to 139.5, in increments of 0.5; for example, 12, 12.5,13,13.5, ……, 139, 139.5.

User Clock 2

User clock 2 is also a divided version of the PMA data rate.

FHT User clock 1 and 2:

In FHT, user clock 2 can be different from user clock 1 if you select a different division factor.

By default, user clock 1 and user clock 2 are disabled; you can enable either or both. The following table shows different combinations of User clock 1 and User clock 2 based on parameters selected in the parameter editor.

| FHT user clk div33_34 select | FHT TX/RX user clk1 select | FHT TX/RX user clk2 select | User clock 1 | User clock 2 |

|---|---|---|---|---|

| DIV_33 | DIV_33_34 | DIV_40 | PMA Data rate / (Number of streams per PMA * 33) | PMA Data rate / (Number of streams per PMA *40) |

| DIV_33 | DIV_40 | DIV_33_34 | PMA Data rate / (Number of streams per PMA *40) | PMA Data rate / (Number of streams per PMA * 33) |

| DIV_34 | DIV_33_34 | DIV_40 | PMA Data rate / (Number of streams per PMA * 34) | PMA Data rate / (Number of streams per PMA * 40 ) |

| DIV_34 | DIV_40 | DIV_33_34 | PMA Data rate / (Number of streams per PMA * 40) | PMA Data rate / (Number of streams per PMA * 34) |

| DIV_66 | DIV_33_34 | DIV_40 | PMA Data rate / (Number of streams per PMA * 66) | PMA Data rate / (Number of streams per PMA * 40) |

| DIV_66 | DIV_40 | DIV_33_34 | PMA Data rate / (Number of streams per PMA * 40) | PMA Data rate / (Number of streams per PMA * 66) |

| DIV_68 | DIV_33_34 | DIV_40 | PMA Data rate / (Number of streams per PMA * 68) | PMA Data rate / (Number of streams per PMA * 40) |

| DIV_68 | DIV_40 | DIV_33_34 | PMA Data rate / (Number of streams per PMA * 40) | PMA Data rate / (Number of streams per PMA * 68) |

FGT User clock 1 and 2:

By default, user clock 1 and user clock 2 are disabled; you can enable either or both. In FGT, user clock 2 is same as user clock 1. The following table shows some example TX/RX user clock div by parameter values. Valid values can range from 12 to 139.5 in increments of 0.5.

| TX/RX user clock div by | User Clock 1 | User Clock 2 |

|---|---|---|

| 33 | VCO Frequency ÷ 33 | VCO Frequency ÷ 33 |

| 34 | VCO Frequency ÷ 34 | VCO Frequency ÷ 34 |

| 66 | VCO Frequency ÷ 66 | VCO Frequency ÷ 66 |

| 68 | VCO Frequency ÷ 68 | VCO Frequency ÷ 68 |

On the TX side of FGT, you can enable user clock 1 and user clock 2 separately. On the RX side, when you enable user clock, it enables both user clock 1 and user clock 2.

The TX and RX clocks for word clock, bond clock, user clock 1, and user clock 2, are two different clocks, derived from TX and RX PMA respectively.

Sys PLL Clock

The Sys PLL clock is the output clock from system PLL. The frequency of this clock is the same as the output frequency of the system PLL connected to the current instance of the F-Tile PMA/FEC Direct PHY Intel® FPGA IP.

Sys PLL Clock Div 2

The Sys PLL clock Div 2 is the output clock from the system PLL, divided by 2. The frequency of this clock is same as the output frequency of the system PLL connected to the current instance of the F-Tile PMA/FEC Direct PHY Intel® FPGA IP, divided by 2.

The Sys PLL clock and Sys PLL clock Div 2 for TX and RX are the same clock and are derived from one system PLL.