AN 866: Mitigating and Debugging Single Event Upsets in Intel® Quartus® Prime Standard Edition

ID

683869

Date

9/28/2021

Public

1.1. Failure Rates

1.2. Mitigating SEU Effects in Embedded User RAM

1.3. Mitigating SEU Effects in Configuration RAM

1.4. Internal Scrubbing

1.5. SEU Recovery

1.6. Intel® Quartus® Prime Software SEU FIT Reports

1.7. Triple-Module Redundancy

1.8. Evaluating a System's Response to Functional Upsets

1.9. CRAM Error Detection Settings Reference

1.10. Document Revision History

1.9. CRAM Error Detection Settings Reference

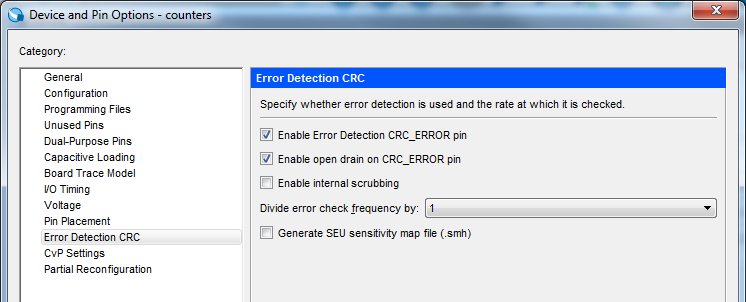

To define these settings in the Intel® Quartus® Prime software, point to Assignments > Device > Device and Pin Options > Error Detection CRC.

Figure 7. Device and Pin Options Error Detection CRC Tab

| Setting | Description |

|---|---|

| Enable Error Detection CRC_ERROR pin | Enables CRAM frame scanning |

| Enable open drain on CRC_ERROR pin | Enables the CRC_ERROR pin as an open-drain output |

| Divide error check frequency by | To guarantee the availability of a clock, the EDCRC function operates on an independent clock generated internally on the FPGA itself. To enable EDCRC operation on a divided version of the clock, select a value from the list. |