Visible to Intel only — GUID: scd1678304366363

Ixiasoft

Visible to Intel only — GUID: scd1678304366363

Ixiasoft

A.1. Protect M20Ks from Spurious Clock Signals during PR Operation

Issue Description

The M20K memory block can lock up if a short pulse (glitch) is applied to the clock port. This can occur during the partial reconfiguration (PR) sequence, when row clocks are manipulated. When this lock up occurs, system failure is likely when attempting to subsequently use the M20K.

Workaround Summary

The Intel® Quartus® Prime Pro Edition software implements a mechanism to assist with this protection by performing logic insertion on the clock enable path of M20K blocks during the Plan stage of the Fitter. This inserted logic must be driven by a signal that you provide that is asserted to logical 1 during the PR operation, and logical 0 at all other times.

You must also identify the signal that you provide by applying the M20K_CE_CONTROL_FOR_PR assignment to the input port for the signal on the corresponding PR partition. You specify this assignment in the .qsf file.

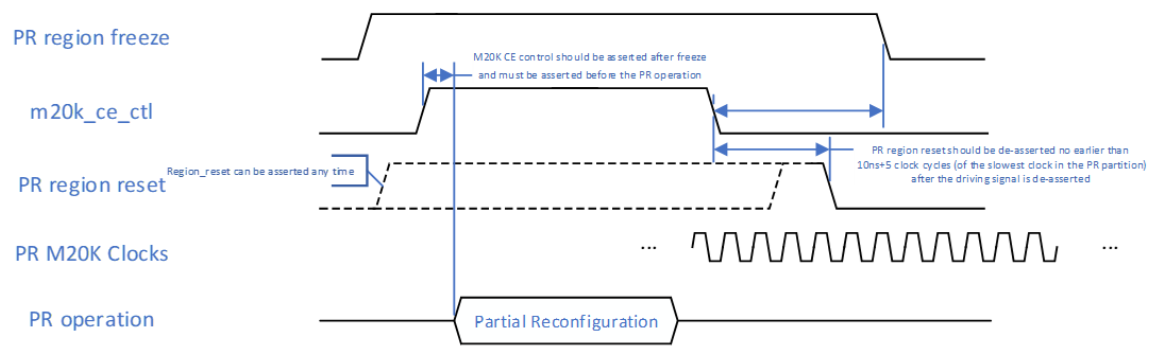

The host controller must assert this signal that you provide during the PR operation, and de-assert this signal after the PR operation. After de-assertion of the this signal, the M20Ks become active after 10ns plus 5 clock cycles of the slowest clock in the PR region. You should only release any freeze logic around the PR region and release the reset of the PR region after this interval, as the following timing diagram illustrates:

If you are using the PR Region Controller Intel FPGA IP, you can also connect this signal that you provide through the IP, or use the PR Region Controller IP CSR registers to control the signal.

The following topics provide more details on implementation for various use cases: