Visible to Intel only — GUID: lbl1453329561675

Ixiasoft

Visible to Intel only — GUID: lbl1453329561675

Ixiasoft

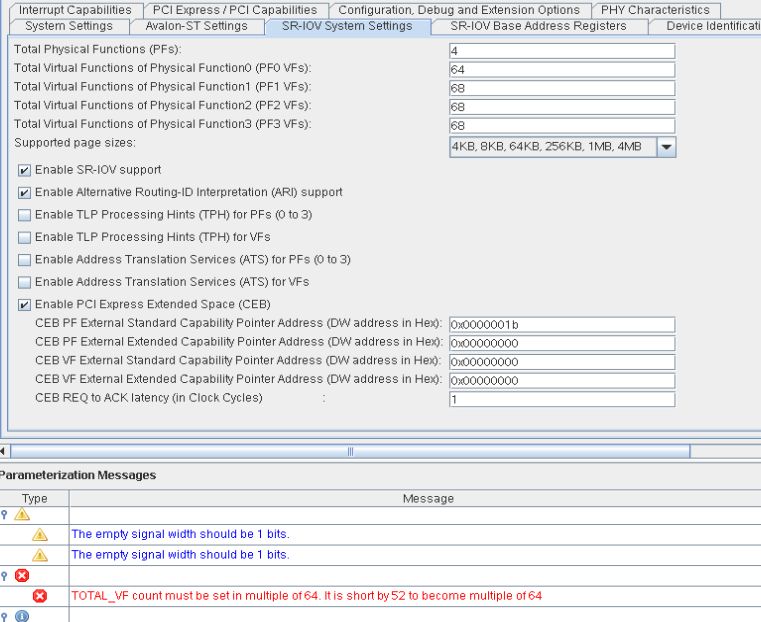

3.3. Arria® 10 SR-IOV System Settings

| Parameter |

Value |

Description |

|---|---|---|

| Total Physical Functions (PFs) : |

1 - 8 |

This core supports 1 - 8 Physical Functions. |

| Total Virtual Functions of Physical Function0 (PF0 VFs) - Total Virtual Functions of Physical Function7 (PF7 VFs): |

0 - 2048 |

Total number of VFs assigned to a PF. You can assign VFs in the following granularities:

Note: The granularity restriction for assigning VFs applies to both the total VFs of each individual PF as well as the sum of all VFs across all enabled PFs. See the example and snapshot following this table for more details.

|

| System Supported Page Size: | 4KB - 4MB | Specifies the pages sizes supported. Sets the Supported Page Sizes register of the SR-IOV Capability structure. |

| Enable SR-IOV Support | On/Off |

When On, the variant supports multiple PFs and VFs. When Off, .supports PFs only. |

| Enable Alternative Routing-ID (ARI) support |

On/Off |

When On, ARI supports up to 256 functions. Refer to Section 6.1.3 Alternative Routing-ID Interpretation (ARI) of the PCI Express Base Specification for more information about ARI. |

| Enable Functional Level Reset (FLR) |

On/Off |

When On, each function has its own, individual reset. |

| Enable TLP Processing Hints (TPH) support for PFs | On/Off | When On, the variant includes the TPH registers to help you improve latency and traffic congestion. |

| Enable TLP Processing Hints (TPH) support for VFs | ||

| Enable Address Translation Services (ATS) support for PFs | On/Off | When On, the variant includes the ATS registers. |

| Enable Address Translation Services (ATS) support for VFs | ||

| Enable PCI Express Extended Space (CEB) | On/Off | When On, the IP core variant includes the optional Configuration Extension Bus (CEB) interface. This interface provides a way to add extra capabilities on top of those available in the internal configuration space of the SR-IOV Bridge.1 |

| CEB PF External Standard Capability Pointer Address (DW Address in Hex) | 0x0 | Specifies the address for the next pointer field of the last capability structure within the SR-IOV bridge for the physical function. It allows the internal PCI Compatible region capability to point to the capability implemented in user logic and establish the link list for the first 256 bytes in the register address space. |

| CEB PF External Extended Capability Pointer Address (DW Address in Hex) | 0x0 | Specifies the address for the next pointer field of the last capability structure within the SR-IOV bridge for the physical function. It allows the internal PCI Compatible region capability to point to the capability implemented in user logic and establish the link list for the PCIe extended configuration space. Supports the address range from 0x100 (DW address) or 0x400 (byte address) and beyond. |

| CEB VF External Standard Capability Pointer Address (DW Address in Hex) | 0x0 | Specifies the address for the next pointer field of the last capability structure within the SR-IOV bridge for the virtual function. It allows the internal PCI Compatible region capability to point to the capability implemented in user logic and establish the link list for the first 256 bytes in the register address space. |

| CEB VF External Extended Capability Pointer Address (DW Address in Hex) | 0x0 | Specifies the address for the next pointer field of the last capability structure within the SR-IOV bridge for the virtual function. It allows the internal PCI Compatible region capability to point to the capability implemented in user logic and establish the link list for the PCIe extended configuration space. Supports the address range from 0x100 (DW address) or 0x400 (byte address) and beyond. |

| CEB REQ to ACK Latency (in Clock Cycles) | 1 - 7 | Specifies the timeout value for the request issued on the CEB interface. The SR-IOV bridge will send a completion with all zeros in the data and completion status field back to the host after the timeout.

Note: A large ACK latency time may result in a bandwidth degradation.

|

The granularity restriction for assigning VFs applies to both the total VFs of each individual PF as well as the sum of all VFs across all enabled PFs. For example, the setting in the snapshot below is invalid since the sum of all VFs assigned to all PFs (i.e, 268 VFs) is not a multiple of 64 and therefore does not meed the granularity restriction even though the VF counts of individual PFs are valid (i.e, they are multiples of 4).