Visible to Intel only — Ixiasoft

2.1. E-Tile Hard IP for Ethernet Intel FPGA IP Supported Features

2.2. E-Tile Hard IP for Ethernet Intel FPGA IP Overview

2.3. IP Core Device Family and Speed Grade Support

2.4. IP Core Verification

2.5. Resource Utilization

2.6. Release Information

2.7. Getting Started

2.8. E-Tile Hard IP for Ethernet Intel FPGA IP Parameters

2.9. Functional Description

2.10. Reset

2.11. Interfaces and Signals

2.12. Register Descriptions

2.13. Document Revision History for the E-tile Hard IP for Ethernet Intel FPGA IP Core

2.9.1. E-Tile Hard IP for Ethernet Intel FPGA IP MAC

2.9.2. 1588 Precision Time Protocol Interfaces

2.9.3. PCS, OTN, FlexE, and Custom PCS Modes

2.9.4. Auto-Negotiation and Link Training

2.9.5. TX and RX RS-FEC

2.9.6. PMA Direct Mode

2.9.7. Dynamic Reconfiguration

2.9.8. Ethernet Adaptation Flow for 10G/25G and 100G/4x25G Dynamic Reconfiguration Design Example

2.9.9. Ethernet Adaptation Flow for 100G (CAUI-2) PAM4 <---> 100G (CAUI-4) NRZ Dynamic Reconfiguration Design Example

2.9.10. Ethernet Adaptation Flow with PTP or with External AIB Clocking

2.9.11. Ethernet Adaptation Flow with Non-external AIB Clocking

2.9.1.2.1. RX Preamble Processing

2.9.1.2.2. RX Strict SFD Checking

2.9.1.2.3. RX FCS Checking

2.9.1.2.4. RX Malformed Packet Handling

2.9.1.2.5. Removing PAD Bytes and FCS Bytes from RX Frames

2.9.1.2.6. RX Undersized Frames, Oversized Frames, and Frames with Length Errors

2.9.1.2.7. Inter-Packet Gap

2.9.2.1. Implementing a 1588 System That Includes a E-Tile Hard IP for Ethernet Intel FPGA IP

2.9.2.2. PTP Timestamp Accuracy

2.9.2.3. PTP Transmit Functionality

2.9.2.4. PTP Receive Functionality

2.9.2.5. External Time-of-Day Module for 1588 PTP Variations

2.9.2.6. PTP Timestamp and TOD Formats

2.9.2.7. 10G/25G TX and RX Unit Interval Adjustment

2.9.2.8. 10G/25G TX and RX PTP Extra Latency

2.9.2.9. 100G PTP TX User Flow

2.9.2.10. 100G PTP RX User Flow

2.9.2.11. 100G RX Virtual Lane Offset Calculation for No FEC Variants

2.9.2.12. 100G UI Adjustment

2.9.2.13. Minimum and Maximum Reference Time (TAM) Interval for UI Measurement (Hardware)

2.9.2.14. PTP System Considerations

2.9.2.15. Logic Lock Regions Requirements for PTP Accuracy Advanced Mode

2.11.1. TX MAC Interface to User Logic

2.11.2. RX MAC Interface to User Logic

2.11.3. TX PCS Interface to User Logic

2.11.4. RX PCS Interface to User Logic

2.11.5. FlexE and OTN Mode TX Interface

2.11.6. FlexE and OTN Mode RX Interface

2.11.7. TX Custom PCS Interface to User Logic

2.11.8. RX Custom PCS Interface to User Logic

2.11.9. PMA Direct Interface

2.11.10. Custom Rate Interface

2.11.11. Deterministic Latency Interface

2.11.12. 1588 PTP Interface

2.11.13. Ethernet Link and Transceiver Signals

2.11.14. Reconfiguration Interfaces and Signals

2.11.15. Miscellaneous Status and Debug Signals

2.11.16. Reset Signals

2.11.17. Clocks

2.11.17.3.1. Single 25G Ethernet Channel (with FEC)

2.11.17.3.2. Single 10G Ethernet Channel (without FEC)

2.11.17.3.3. Four 25G Ethernet Channels (with FEC) within a Single FEC Block

2.11.17.3.4. Ethernet 25G x 4 (FEC Off)

2.11.17.3.5. 10G/25G Ethernet Channel with Basic PTP Accuracy Mode

2.11.17.3.6. 10G/25G Ethernet Channel with Advanced PTP Accuracy Mode

2.11.17.3.7. 100G Ethernet with Aggregated FEC

2.11.17.3.8. 100G Ethernet with PTP

2.11.17.3.9. Single 25G Synchronous Ethernet Channel

2.11.17.3.10. Multiple 25G Synchronous Ethernet Channels

2.12.1. Auto Negotiation and Link Training Registers

2.12.2. PHY Registers

2.12.3. TX MAC Registers

2.12.4. RX MAC Registers

2.12.5. Pause and Priority- Based Flow Control Registers

2.12.6. TX Statistics Counter Registers

2.12.7. RX Statistics Counter Registers

2.12.8. 1588 PTP Registers

2.12.9. RS-FEC Registers

2.12.10. PMA Registers

2.12.1.1. ANLT Sequencer Config

2.12.1.2. ANLT Sequencer Status

2.12.1.3. Auto Negotiation Config Register 1

2.12.1.4. Auto Negotiation Config Register 2

2.12.1.5. Auto Negotiation Status Register

2.12.1.6. Auto Negotiation Config Register 3

2.12.1.7. Auto Negotiation Config Register 4

2.12.1.8. Auto Negotiation Config Register 5

2.12.1.9. Auto Negotiation Config Register 6

2.12.1.10. Auto Negotiation Status Register 1

2.12.1.11. Auto Negotiation Status Register 2

2.12.1.12. Auto Negotiation Status Register 3

2.12.1.13. Auto Negotiation Status Register 4

2.12.1.14. Auto Negotiation Status Register 5

2.12.1.15. AN Channel Override

2.12.1.16. Consortium Next Page Override

2.12.1.17. Consortium Next Page Link Partner Status

2.12.1.18. Link Training Config Register 1

2.12.1.19. Link Training Status Register 1

2.12.1.20. Link Training Config Register for Lane 0

2.12.1.21. Link Training Config Register for Lane 1

2.12.1.22. Link Training Config Register for Lane 2

2.12.1.23. Link Training Config Register for Lane 3

2.12.2.1. PHY Module Revision ID

2.12.2.2. PHY Scratch Register

2.12.2.3. Loopback Mode

2.12.2.4. PHY Configuration

2.12.2.5. Reset Sequencer RS-FEC Disable

2.12.2.6. RX CDR PLL Locked

2.12.2.7. TX Datapath Ready

2.12.2.8. Frame Errors Detected

2.12.2.9. Clear Frame Errors

2.12.2.10. RX PCS Status for AN/LT

2.12.2.11. PCS Error Injection

2.12.2.12. Alignment Marker Lock

2.12.2.13. Change in RX PCS Deskew Status

2.12.2.14. BER Count

2.12.2.15. Transfer Ready (AIB reset) Status for EHIP, ELANE, and PTP Channels

2.12.2.16. EHIP, ELANE, and RS-FEC Reset Status

2.12.2.17. PCS Virtual Lane 0

2.12.2.18. PCS Virtual Lane 1

2.12.2.19. PCS Virtual Lane 2

2.12.2.20. PCS Virtual Lane 3

2.12.2.21. Recovered Clock Frequency in KHz

2.12.2.22. TX Clock Frequency in KHz

2.12.2.23. Configuration Fields for TX PLD

2.12.2.24. Status for TX PLDs

2.12.2.25. Status for Dynamic Deskew Buffer

2.12.2.26. Configuration for RX PLD Block

2.12.2.27. Configuration for RX PCS

2.12.2.28. BIP Counter 0

2.12.2.29. BIP Counter 1

2.12.2.30. BIP Counter 2

2.12.2.31. BIP Counter 3

2.12.2.32. BIP Counter 4

2.12.2.33. BIP Counter 5

2.12.2.34. BIP Counter 6

2.12.2.35. BIP Counter 7

2.12.2.36. BIP Counter 8

2.12.2.37. BIP Counter 9

2.12.2.38. BIP Counter 10

2.12.2.39. BIP Counter 11

2.12.2.40. BIP Counter 12

2.12.2.41. BIP Counter 13

2.12.2.42. BIP Counter 14

2.12.2.43. BIP Counter 15

2.12.2.44. BIP Counter 16

2.12.2.45. BIP Counter 17

2.12.2.46. BIP Counter 18

2.12.2.47. BIP Counter 19

2.12.2.48. Timer Window for Hi-BER Checks

2.12.2.49. Hi-BER Frame Errors

2.12.2.50. Error Block Count

2.12.2.51. Deskew Depth 0

2.12.2.52. Deskew Depth 1

2.12.2.53. Deskew Depth 2

2.12.2.54. Deskew Depth 3

2.12.2.55. RX PCS Test Error Count

2.12.3.1. TX MAC Module Revision ID

2.12.3.2. TX MAC Scratch Register

2.12.3.3. Link Fault Configuration

2.12.3.4. IPG Words to remove per Alignment Marker Period

2.12.3.5. Maximum TX Frame Size

2.12.3.6. TX MAC Configuration

2.12.3.7. EHIP TX MAC Feature Configuration

2.12.3.8. TX MAC Source Address Lower Bytes

2.12.3.9. TX MAC Source Address Higher Bytes

2.12.5.1. TXSFC Module Revision ID

2.12.5.2. TX SFC Scratch Register

2.12.5.3. Enable TX Pause Ports

2.12.5.4. TX Pause Request

2.12.5.5. Enable Automatic TX Pause Retransmission

2.12.5.6. Retransmit Holdoff Quanta

2.12.5.7. Retransmit Pause Quanta

2.12.5.8. Enable TX XOFF

2.12.5.9. Enable Uniform Holdoff

2.12.5.10. Set Uniform Holdoff

2.12.5.11. Lower 4 bytes of the Destination address for Flow Control

2.12.5.12. Higher 2 bytes of the Destination address for Flow Control

2.12.5.13. Lower 4 bytes of the Source address for Flow Control frames

2.12.5.14. Higher 2 bytes of the Source address for Flow Control frames

2.12.5.15. TX Flow Control Feature Configuration

2.12.5.16. Pause Quanta 0

2.12.5.17. Pause Quanta 1

2.12.5.18. Pause Quanta 2

2.12.5.19. Pause Quanta 3

2.12.5.20. Pause Quanta 4

2.12.5.21. Pause Quanta 5

2.12.5.22. Pause Quanta 6

2.12.5.23. Pause Quanta 7

2.12.5.24. PFC Holdoff Quanta 0

2.12.5.25. PFC Holdoff Quanta 1

2.12.5.26. PFC Holdoff Quanta 2

2.12.5.27. PFC Holdoff Quanta 3

2.12.5.28. PFC Holdoff Quanta 4

2.12.5.29. PFC Holdoff Quanta 5

2.12.5.30. PFC Holdoff Quanta 6

2.12.5.31. PFC Holdoff Quanta 7

2.12.5.32. RXSFC Module Revision ID

2.12.5.33. RXSFC Scratch Register

2.12.5.34. Enable RX Pause Frame Processing

2.12.5.35. Forward Flow Control Frames

2.12.5.36. Lower 4 bytes of the Destination address for RX Pause Frames

2.12.5.37. Higher 2 bytes of the Destination address for RX Pause Frames

2.12.5.38. RX Flow Control Feature Configuration

3.1. Supported Features

3.2. E-Tile CPRI PHY Intel® FPGA IP Overview

3.3. E-Tile CPRI PHY Device Family Support

3.4. Resource Utilization

3.5. Release Information

3.6. E-Tile CPRI PHY Intel FPGA IP Core Device Speed Grade Support

3.7. Getting Started

3.8. Parameter Settings

3.9. Functional Description

3.10. E-Tile CPRI PHY Intel FPGA IP Interface Signals

3.11. Registers

3.12. Document Revision History for the E-tile CPRI PHY Intel FPGA IP

Visible to Intel only — Ixiasoft

2.7.4.1.1. Guidelines and Restrictions for 24-bonded Channels Variant

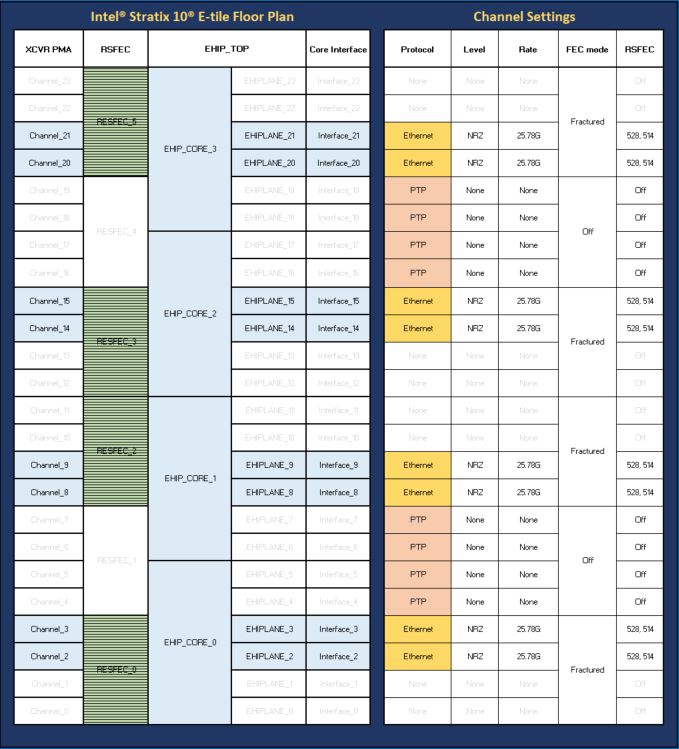

The E-tile transceiver requires the channel placement to be contiguous when RS-FEC is enabled. The following are the allowed channel placements for different number of channels.

Single Channel 10GE/25GE with RS-FEC Variant

Following are the parameter settings for these channel placements:

- Select Core Variant: 1 to 4 10GE/25GE with optional RSFEC

- Number of Channels of 10GE/25GE: Single Channel

- Enable RSFEC: Selected

- First RSFEC Lane: first_lane0(channel_0), first_lane1(channel_5), first_lane2(channel_10), or first_lane3(channel_15)

- The FEC mode is set to fractured mode.

Two Channels 10GE/25GE with RS-FEC Variant

Following are the parameter settings for these channel placements:

- Select Core Variant: 1 to 4 10GE/25GE with optional RSFEC

- Number of Channels of 10GE/25GE: 2 Channels

- Enable RSFEC: Selected

- First RSFEC Lane: first_lane0(channel_0), first_lane1(channel_5), or first_lane2(channel_10)

- The FEC mode is set to fractured mode.

Three Channels 10GE/25GE with RS-FEC

Following are the parameter settings for these channel placements:

- Select Core Variant: 1 to 4 10GE/25GE with optional RSFEC

- Number of Channels of 10GE/25GE: 3 Channels

- Enable RSFEC: Selected

- First RSFEC Lane: first_lane0(channel_0) or first_lane1(channel_5)

- The FEC mode is set to fractured mode.

Four Channels 10GE/25GE with RS-FEC Variant

Following are the parameter settings for these channel placements:

- Select Core Variant: 1 to 4 10GE/25GE with optional RSFEC

- Number of Channels of 10GE/25GE: 4 Channels

- Enable RSFEC: Selected

- First RSFEC Lane: first_lane0(channel_0)

- The FEC mode is set to fractured mode.

100GE with RS-FEC Variant

You can use the following channel placements for a four-channel Native PHY with single RS-FEC block without PTP variant.

In 100GE tab, Select Ethernet IP Layers: MAC+PCS+RSFEC.

Following are the IP tab parameter settings for these channel placements:

- Select Core Variant: Single 100GE with optional RSFEC

- Enable RSFEC: Selected

- The FEC mode is set to aggregate mode.

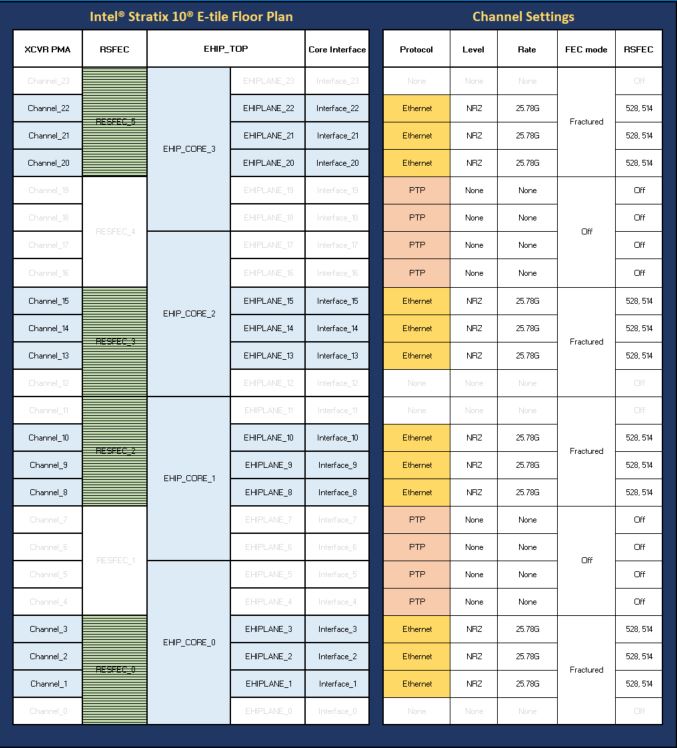

Single Channel 10GE/25GE with RS-FEC and PTP Variant

When RS-FEC and PTP are enabled, place the RS-FEC channel next to the PTP channels. The supported PTP channel locations for this variant are:

- Channel_4/5 when using EHIP_CORE0

- Channel 6/7 when using EHIP_CORE1

- Channel 16/17 when using EHIP_CORE2

- Channel 18/19 when using EHIP_CORE3

Following are the parameter settings for these channel placements:

- Select Core Variant: 100GE or 1 to 4 10GE/25GE with optional RSFEC and 1588 PTP

- Number of Channels of 10GE/25GE: Single Channel

- Active Channel(s) at startup: 10G/25GE Channel(s)

- Enable IEEE 1588 PTP: Selected

- Enable RSFEC: Selected

- When IEEE1588/PTP channel placement restriction is set to EHIP0/2(EHIP_CORE_0/EHIP_CORE2), the First RSFEC Lane should set to first_lane3(channel_3 or channel_15).

- When IEEE1588/PTP channel placement restriction is set to EHIP1/3(EHIP_CORE_1/EHIP_CORE3), the First RSFEC Lane should set to first_lane0(channel_8 or channel_20).

- The FEC mode is set to fractured mode.

Two Channels 10GE/25GE with RS-FEC and PTP Variant

When RS-FEC and PTP are enabled, place the RS-FEC channel next to the PTP channels. The supported PTP channel locations for this variant are:

- Channel_4/5 when using EHIP_CORE0

- Channel 6/7 when using EHIP_CORE1

- Channel 16/17 when using EHIP_CORE2

- Channel 18/19 when using EHIP_CORE3

Following are the parameter settings for these channel placements:

- Select Core Variant: 100GE or 1 to 4 10GE/25GE with optional RSFEC and 1588 PTP

- Number of Channels of 10GE/25GE: 2 Channels

- Active Channel(s) at startup: 10G/25GE Channel(s)

- Enable IEEE 1588 PTP: Selected

- Enable RSFEC: Selected

- When IEEE1588/PTP channel placement restriction is set to EHIP0/2(EHIP_CORE_0/EHIP_CORE2), the First RSFEC Lane should set to first_lane2.

- When IEEE1588/PTP channel placement restriction is set to EHIP1/3(EHIP_CORE_1/EHIP_CORE3), the First RSFEC Lane should set to first_lane0(channel_8 or channel_20).

- The FEC mode is set to fractured mode.

Three Channels 10GE/25GE with RS-FEC and PTP Variant

When RS-FEC and PTP are enabled, place the RS-FEC channel next to the PTP channels. The supported PTP channel locations for this variant are:

- Channel_4/5 when using EHIP_CORE0

- Channel 6/7 when using EHIP_CORE1

- Channel 16/17 when using EHIP_CORE2

- Channel 18/19 when using EHIP_CORE3

Following are the parameter settings for these channel placements:

- Select Core Variant: 100GE or 1 to 4 10GE/25GE with optional RSFEC and 1588 PTP

- Number of Channels of 10GE/25GE: 3 Channels

- Active Channel(s) at startup: 10G/25GE Channel(s)

- Enable IEEE 1588 PTP: Selected

- Enable RSFEC: Selected

- When IEEE1588/PTP channel placement restriction is set to EHIP0/2(EHIP_CORE_0/EHIP_CORE2), the First RSFEC Lane should set to first_lane1(channel_3 or channel_15).

- When IEEE1588/PTP channel placement restriction is set to EHIP1/3(EHIP_CORE_1/EHIP_CORE3), the First RSFEC Lane should set to first_lane0(channel_8 or channel_20).

- The FEC mode is set to fractured mode.

Four Channels 10GE/25GE with RS-FEC and PTP Variant

When RS-FEC and PTP are enabled, place the RS-FEC channel next to the PTP channels. The supported PTP channel locations for this variant are:

- Channel_4/5 when using EHIP_CORE0

- Channel 6/7 when using EHIP_CORE1

- Channel 16/17 when using EHIP_CORE2

- Channel 18/19 when using EHIP_CORE3

Following are the parameter settings for these channel placements:

- Select Core Variant: 100GE or 1 to 4 10GE/25GE with optional RSFEC and 1588 PTP

- Number of Channels of 10GE/25GE: 4 Channels

- Active Channel(s) at startup: 10G/25GE Channel(s)

- Enable IEEE 1588 PTP: Selected

- Enable RSFEC: Selected

- IEEE1588/PTP channel placement restriction: EHIP0/2(EHIP_CORE_0/EHIP_CORE2) or EHIP1/3(EHIP_CORE_1/EHIP_CORE3)

- First RSFEC Lane: first_lane0

- The FEC mode is set to fractured mode.