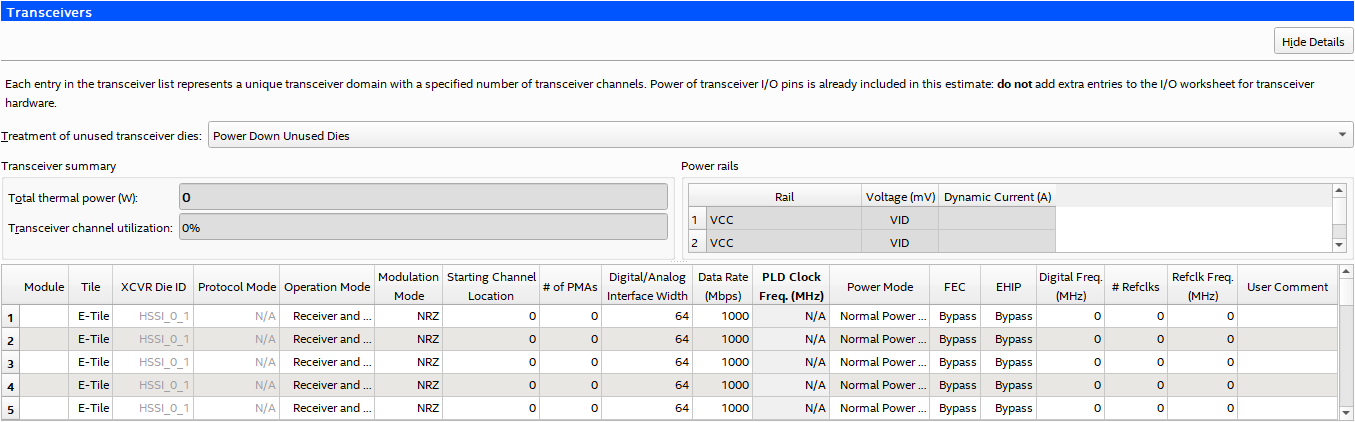

4.12. Intel® FPGA PTC - Transceiver Page

| Input Parameter | Description |

|---|---|

| Total Thermal Power (W) | Total power dissipated in all modules on this page (in watts). |

| Treatment of Unused HSSI Dies |

|

Each row in the Transceiver page represents a separate transceiver domain. Enter the following parameters for each transceiver domain:

| Column Heading | Description |

|---|---|

| Module | Specifies a name for the module. This is an optional value. |

| Tile | Specifies the type of transceiver die on which transceiver channels are located. Some devices may include more than one type of transceiver die. This field changes depending on the device options that you choose on the Main page. |

| XCVR Die ID | Specify the transceiver die on which transceiver channels on this row are located. |

| Protocol Mode | Specifies the mode in which the PCS, HIP, and PCIE blocks operate. This mode depends on the XCVR tile and the communication protocol or standard that the channels on this row implement. |

| Operation Mode | Specifies whether the hardware is configured in full duplex transceiver mode (receiver and transmitter), Receiver Only mode, or Transmitter Only mode. Allowed values depend on the selected tile and protocol mode. |

| Modulation Mode | Specify the data modulation mode of transceiver channels. This field is applicable only to E-Tile transceivers. When you select High Data Rate PAM4 for this field, 2 physical channels are paired to represent 1 logical channel. When specifying # of Channels, enter the number of physical channels (that is, in multiples of 2). |

| Starting Channel Location | Specify the starting location within the die for the channels specified in this row. For example, if a given row contains 3 channels, and starting location is specified to be 12, channels are assumed to be in locations 12, 13, and 14. Location 0 denotes the bottom-most channel on the transceiver die. |

| # of PMAs | Specifies the number of physical medium attachments (PMAs) used in this transceiver domain. Each row represents one transceiver domain. These PMAs are grouped together in one transceiver bank, or two or more adjacent transceiver banks and clocked by one or more common transmitter PLLs. For E-tile transceivers, if the selected modulation mode is High Data Rate PAM4, enter 2 physical channels to represent 1 logical channel. ( Intel® Agilex™ devices only.) For F-tile transceivers:

For more information about PMAs and streams, refer to the F-tile Architecture and PMA and FEC Direct PHY IP User Guide. |

| # of Channels | Specifies the number of channels used in this transceiver domain. Each row represents one transceiver domain. These channels are grouped together in one transceiver bank, or two or more adjacent transceiver banks and clocked by one or more common transmitter PLLs. For E-tile transceivers, if the selected modulation mode is High Data Rate PAM4, enter 2 physical channels to represent 1 logical channel. ( Intel® Stratix® 10 devices only.) |

| Digital/Analog Interface Width | Specify the width of the parallel data bus between PCS and PMA. For E-tile PMA Direct, set to PMA parallel data width, even if FPGA FIFO widens the interface. As an example, for 25 Gbps PMA Direct you would typically set this value to 32. When the FEC or EHIP is used, you would set this value to 32 for NRZ mode and 64 for PAM4 mode. |

| Data Rate (Mbps) | Specifies the data rate (in Mbps) for the transceiver. Allowed values depend on the selected protocol mode and selected device. |

| PLD Clock Frequency (MHz) | Specifies the PLD clock frequency. This is applicable only to P-tile transceivers, and when the selected protocol is PCIe gen4. |

| Power Mode | E-tile transceivers can operate at either Normal Power Mode or Low Power Mode. For thermal analysis and regulator sizing, you must set the E-tile transceivers in the Normal Power Mode, because your board design must take into consideration the maximum power conditions. Refer to the E-tile Transceiver PHY User Guide for information on how to switch transceivers from Normal Power Mode to Low Power Mode. |

| FEC | Specify the Forward Error Correction setting. This field is applicable only to E-Tile transceivers. |

| EHIP | Specify the Ethernet Hard IP protocol. This field is applicable only to E-Tile and F-Tile transceivers. |

| Digital Frequency (MHz) | Specify the digital frequency at which the digital portion of the transceiver (including FEC and EHIP) operates. This field is applicable only to E-tile transceivers. |

| # Refclks | Specify the number of reference clocks in use. If another interface on this tile is using the same reference clock, and you have already entered this clock in another row, enter 0 in this row to avoid double counting. This field is applicable only to E-Tile transceivers. |

| Refclk Frequency (MHz) | Specify the reference clock frequency. This field is applicable only to E-Tile and F-Tile transceivers. |

| Application | Specify the application type, which determines values for advanced channel options. Select Custom to enable manual editing of advanced channel options for the current row. This field is applicable only to L-tile and H-tile transceivers. |

| VCCR_GXB and VCCT_GXB Voltage | Specifies the voltage of the VCCR_GXB and VCCT_GXB rails. Allowed values depend on the selected device and selected data rate. This field is applicable only to L-tile and H-tile transceivers. |

| VOD Setting | The output differential voltage (VOD) setting of the transmitter channel PMA. To enable this setting, select Custom in the Application column. This field is applicable only to L-tile and H-tile transceivers. |

| VOD Voltage | The output differential voltage (VOD) of the transmitter channel PMA (in mV). This voltage depends on the VOD setting and the VCCT_GXB voltage. This field is applicable only to L-tile and H-tile transceivers. |

| First Pre-Tap | Specifies the pre-emphasis setting used by the transmitter channel PMA. Set to Off if the tap value is 0; otherwise, set to On. If pre-emphasis settings are set to On, power consumption does not depend on the magnitude nor the sign (positive or negative) of individual taps. To enable these settings, select Custom in the Application column. |

| First Post-Tap | |

| DFE | Specify mode of the decision feedback equalizer (DFE). Allowed values depend on the selected data rate. To enable this setting, select Custom in the Application column. This field is applicable only to L-tile and H-tile transceivers. |

| Adaptation | Specify if the adaptation feature is used. This option should be enabled if the channels use either CTLE adaptation or DFE adaptation. To enable this setting, select Custom in the Application column. This field is applicable only to L-tile and H-tile transceivers. |

| Transmitter High-Speed Compensation | Specifies if the power distribution network (PDN) induced inter-symbol interference (ISI) compensation is enabled in the TX driver. To enable this setting, select Custom in the Application column. This field is applicable only to L-tile and H-tile transceivers. |

| User Comments | Enter any comments. This is an optional entry. |

For more information about the transceiver architecture of the supported device families, refer to the appropriate Transceiver PHY User Guide for Intel® Agilex™ devices.