Visible to Intel only — GUID: qeg1572268092241

Ixiasoft

1. Overview of the Intel® FPGA Power and Thermal Calculator

2. Setting Up the Intel® FPGA Power and Thermal Calculator

3. Intel® FPGA Power and Thermal Calculator Graphical User Interface

4. Intel® FPGA Power and Thermal Calculator Pages

5. Factors Affecting the Accuracy of the Intel® FPGA Power and Thermal Calculator

6. Intel® FPGA Power and Thermal Calculator User Guide Archive

7. Document Revision History for the Intel® FPGA Power and Thermal Calculator User Guide

A. Measuring Static Power

4.1. Intel® FPGA PTC - Power Summary

4.2. Intel® FPGA PTC - Common Page Elements

4.3. Intel® FPGA PTC - Device Selection and Thermal Analysis Windows

4.4. Intel® FPGA PTC - Main Page

4.5. Intel® FPGA PTC - Logic Page

4.6. Intel® FPGA PTC - RAM Page

4.7. Intel® FPGA PTC - DSP Page

4.8. Intel® FPGA PTC - Clock Page

4.9. Intel® FPGA PTC - PLL Page

4.10. Intel® FPGA PTC - I/O Page

4.11. Intel® FPGA PTC - I/O-IP Page

4.12. Intel® FPGA PTC - Transceiver Page

4.13. Intel® FPGA PTC - HPS Page

4.14. Intel® FPGA PTC - Crypto Page ( Intel® Agilex™ Devices with Crypto Blocks Only)

4.15. Intel® FPGA PTC - HBM Page ( Intel® Stratix® 10 Devices Only)

4.16. Intel® FPGA PTC - Thermal Page

4.17. Intel® FPGA PTC - Report Page

Visible to Intel only — GUID: qeg1572268092241

Ixiasoft

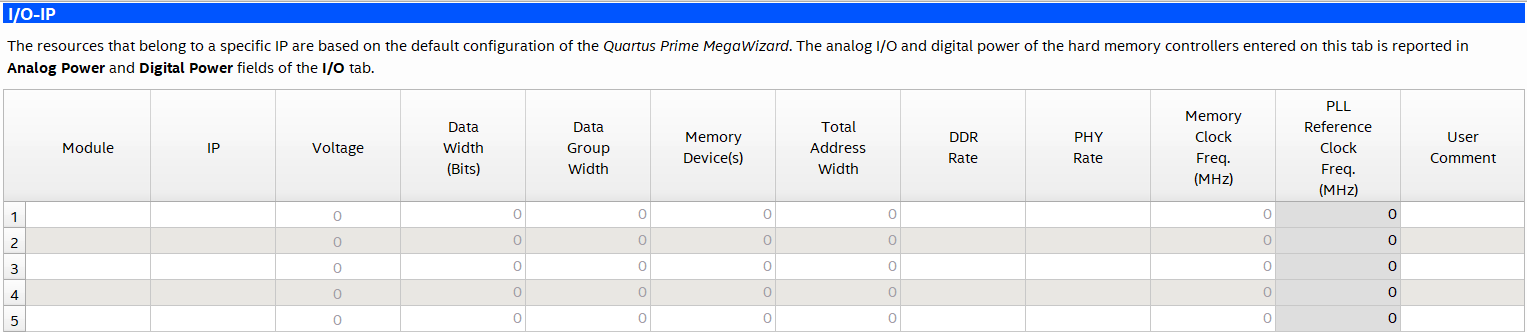

4.11. Intel® FPGA PTC - I/O-IP Page

Each row in the I/O-IP page of the Intel® FPGA Power and Thermal Calculator ( Intel® FPGA PTC) represents a design module. You can use the I/O-IP page to instantiate external memory interface and HPS IPs supported by the target device. The I/O-IP page populates other Intel® FPGA PTC pages with resources used by a selected IP.

Analog I/O power and digital power of hard memory controllers and HPS IPs entered on this page are reported in the Analog Power and Digital Power fields of the I/O page. If the IP uses other resource types (for example Logic or PLL), the power is reported on the corresponding page.

Figure 20. I/O-IP Page of the Intel® FPGA PTC

I/O-IP Page Information

| Column Heading | Description |

|---|---|

| Module | Specifies a name for the IP in this column. The module name depends on the selected IP type. It helps to cross-reference each IP module and its corresponding auto-populated entries on other pages. This name is auto-populated when IP type is selected in the IP column and cannot be changed. |

| IP | Specifies the type of the IP in the design. |

| Voltage | Specifies the I/O voltage of the signaling between periphery device and interface. |

| Data Width (Bits) | Specifies the interface data width of the specific IP (in bits). |

| # of DQS Groups | Specifies the number of DQS groups. |

| Memory Device(s) | Specifies the number of memory devices connected to the interface. |

| Total Address Width | Specifies the total address width. This value is used to derive the total number of address pins required. |

| DDR Rate | Specifies the clock rate of user logic. Determines the clock frequency of user logic in relation to the memory clock frequency. For example, if the memory clock sent from the FPGA to the memory device is toggling at 800MHz, a "Quarter rate" interface means that the user logic in the FPGA runs at 200MHz. |

| PHY Rate | Specifies the clock rate of PHY logic. Determines the clock frequency of PHY logic in relation to the memory clock frequency. For example, if the memory clock sent from the FPGA to the memory device is toggling at 800MHz, a "Quarter rate" interface means that the PHY logic in the FPGA runs at 200MHz. |

| Memory Clock Frequency (MHz) | Specifies the frequency of memory clock (in MHz). |

| PLL Reference Clock Frequency (MHz) | Reports the PLL Reference Clock Frequency (in MHz). |

| User Comments | Enter any comments. This is an optional entry. |