Visible to Intel only — GUID: mwh1410471059421

Ixiasoft

1.1.2.1. Specify Instance-Specific Constraints in Assignment Editor

1.1.2.2. Specify NoC Constraints in NoC Assignment Editor

1.1.2.3. Specify Dual Simplex Assignments in DS Assignment Editor

1.1.2.4. Specify I/O Constraints in Pin Planner

1.1.2.5. Plan Interface Constraints in Interface Planner and Tile Interface Planner

1.1.2.6. Adjust Constraints with the Chip Planner

1.1.2.7. Constraining Designs with the Design Partition Planner

3.2.1. Assigning to Exclusive Pin Groups

3.2.2. Assigning Slew Rate and Drive Strength

3.2.3. Assigning I/O Banks

3.2.4. Changing Pin Planner Highlight Colors

3.2.5. Showing I/O Lanes

3.2.6. Assigning Differential Pins

3.2.7. Entering Pin Assignments with Tcl Commands

3.2.8. Entering Pin Assignments in HDL Code

Visible to Intel only — GUID: mwh1410471059421

Ixiasoft

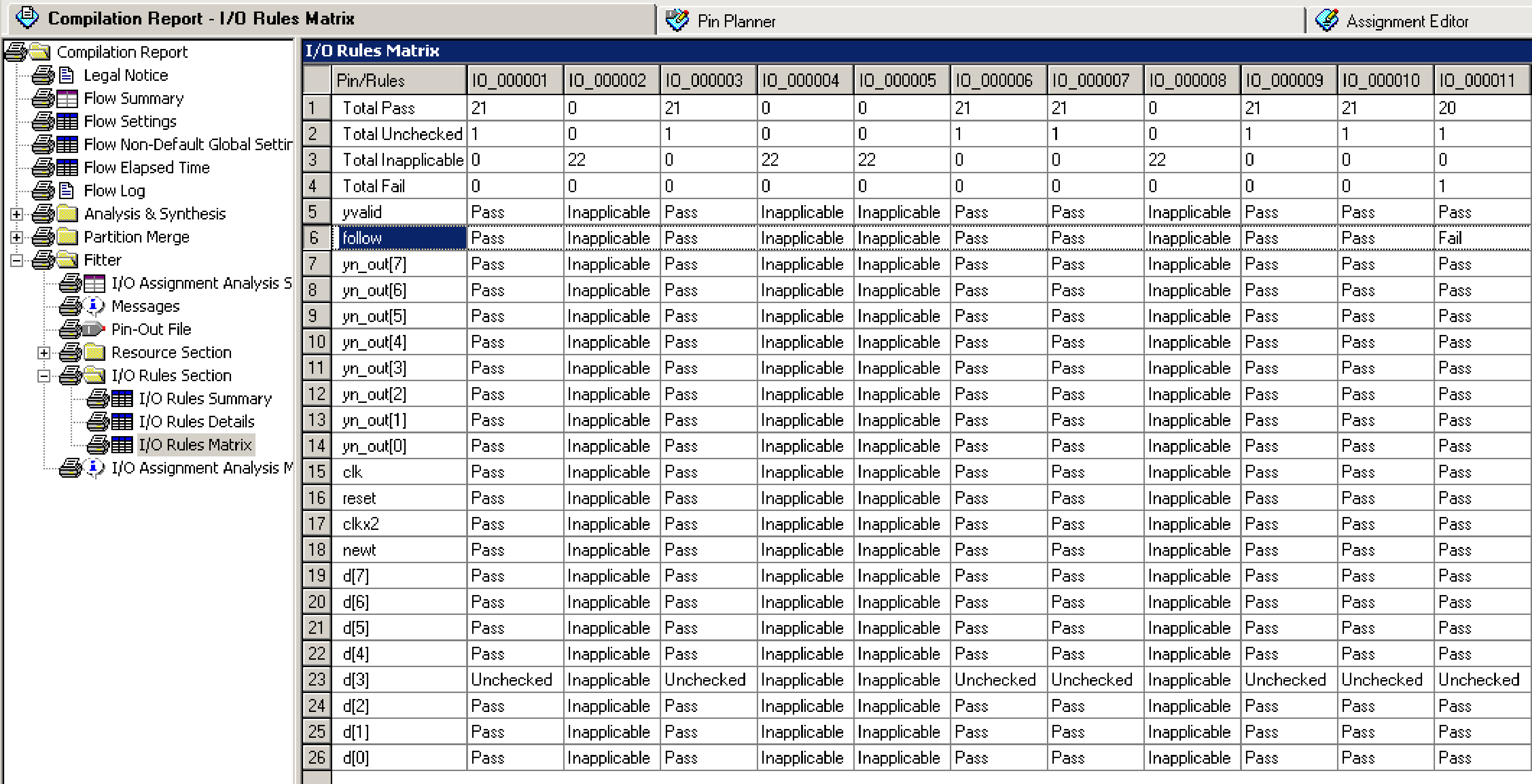

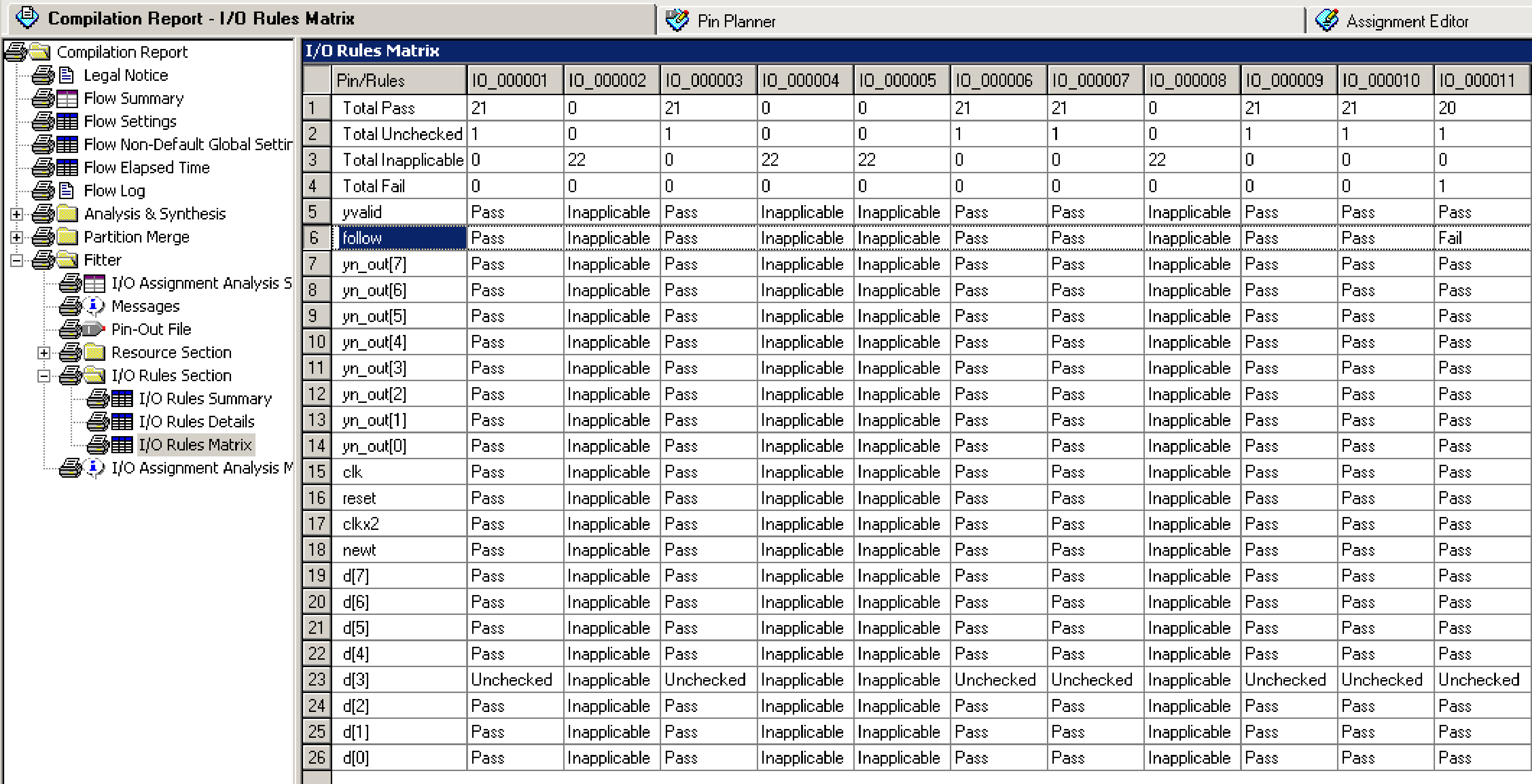

3.4.3. Understanding I/O Analysis Reports

The detailed I/O assignment analysis reports include the affected pin name and a problem description. The Fitter section of the Compilation report contains information generated during I/O assignment analysis, including the following reports:

- I/O Assignment Warnings—lists warnings generated for each pin

- Resource Section—quantifies use of various pin types and I/O banks

- I/O Rules Section—lists summary, details, and matrix information about the I/O rules tested

The Status column indicates whether rules passed, failed, or were not checked. A severity rating indicates the rule’s importance for effective analysis. “Inapplicable” rules do not apply to the target device family.

Figure 75. I/O Rules Matrix