A newer version of this document is available. Customers should click here to go to the newest version.

Visible to Intel only — GUID: msi1669754788934

Ixiasoft

Visible to Intel only — GUID: msi1669754788934

Ixiasoft

7.12.1. Deterministic Latency Measurement

Deterministic Latency (DL) is the ability to precisely determine the delay between the FPGA core and the serial pins. In most applications, the variability is acceptable to determine the actual delay within a given reset session. This section provides an example that shows the calculation delay between pins and FPGA core for the F-Tile Ethernet Intel® FPGA Hard IP core.

The Deterministic Latency Interface is an option in which the signals required for latency calculation are exposed to the top of the IP and you need to write RTL logic to measure it.

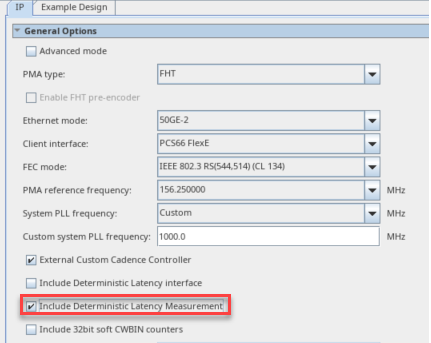

The Deterministic Latency Measurement is an option in which the F-Tile Ethernet Intel® FPGA Hard IP performs the measurement calculations and store the values in soft registers. You can obtain the latency values by directly accessing the soft CSR registers.

When the deterministic latency measurement is enabled, you can calculate the latency using the deterministic latency factors listed below.

| Factor | Description |

|---|---|

| TxDL | Transmitter delay in i_sampling_clock cycle. To calculate the TxDL value, read the DL soft register 0x314 bit[20:0]. The register provides the value in fixed point format. Bit[20:8] represents an integer, and bit[7:0] represents a fractional number.

For example:

Note: These values are available in simulation output.

|

| RxDL | Receiver delay in i_sampling_clock cycle. To calculate the RxDL value, read the DL soft register 0x318 bit [20:0]. The register provides a value in fixed point format. Bit[20:8] represents an integer, and bit[7:0] represents a fractional number.

For example:

Note: These values are available in simulation output.

|

| i_sampling_clock_period | For F-Tile Ethernet Intel FPGA Hard IP core:

|

| eth_wa | Obtained from the Datapath Avalon Memory-Mapped Interface register 0x1110[6:0]. |

| ethlphy_wa | RS-FEC codeword bit position on Rx value (lowest 5 bit) obtained from the Datapath Avalon Memory-Mapped Interface register 0x6174[4:0]. |

| dlpulse | Obtained from the Datapath Avalon Memory-Mapped Interface register 0x1110[7]. |

| Latency (ns) | For 25GE/50GE/100GE/200GE/400GE with RS-FEC Variants | For 10GE/25GE/50GE/100GE without RS-FEC variants |

|---|---|---|

| TX | TxDL * 4ns + 6 * o_clk_pll_period + TX_PMA_Delay * UI_value | |

| RX | RxDL * 4ns - 6 * o_clk_pll_period + (RX_PMA_Delay - ethlphy_wa) * UI_value | RxDL * 4ns - 6 * o_clk_pll_period + (RX_PMA_Delay - eth_wa - 33 * dlpulse)* UI_value |

- TxDL

- RxDL

- ethlphy_wa

- eth_wa

- dlpulse

For TX_PMA_Delay, RX_PMA_Delay and UI_value, refer to the UI Value and PMA Delay.