Visible to Intel only — GUID: nmq1716197778174

Ixiasoft

Visible to Intel only — GUID: nmq1716197778174

Ixiasoft

1. About the Drive-on-Chip with Functional Safety Design Example for Agilex™ 7 Devices

Altera does not intend you to certify the design. Therefore, Altera only applies the safety design process described in IEC 61508 only where relevant. The design shows how you apply the Altera SoC FPGA Cat 3 PL d and SIL 2 safety concept. The architecture is based around a particular component of the drive-on-chip, the speed limit. You can extend the concept to monitor, cross-compare, and control other relevant physical and logical variables that are key for safety.

This design demonstrates synchronous control of up to two three-phase permanent magnet synchronous motors (PMSMs) or brushless DC (BLDC) motors. The design includes a motor and power board model that removes the need for a physical motor setup.

This design is an extension of the existing Drive-on-Chip Design Example for Agilex™ 7 Devices. It includes safety function to demonstrate how Agilex™ 7 SoC devices may achieve IEC 61508 SIL 2 or ISO 13849 Cat 3 PL d safety certification.

You need an Agilex™ 7 F-series FPGA Development Kit to run the design. The motor and power model helps you tune and test the control system before using a physical power stage. The motor and power board model are based on the former Tandem Motion 48 V board, described in AN 994 Drive-on-Chip Design Example for Agilex™ 7 Devices.

Supported FPGA Development Kits

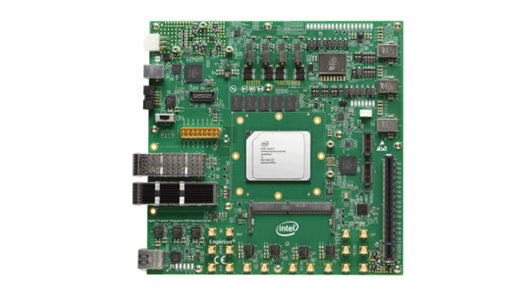

The design supports the Rev C (or later) Agilex 7 F-series Transceiver-SoC (AGFB014R24B2E2EV) (DK-SI-AGF014EA) FPGA Development Kit. You can modify the design to run it on other FPGA development kits.

Supported Motor Control Boards

The motor and power board model is based on Tandem Motion 48V power boards. You can parameterize the design to operate with various physical motors and power boards. However, since the example design is shipped with a power board and motor emulation model, physical motors or a power board is not needed to run this example, only the development kit.

Agilex 7 Devices and DSP Builder for Intel FPGAs.

Agilex 7 devices offer high-performance fixed- and floating-point DSP functionality, and the possibility to instance Nios V/g soft processors. FPGA devices offer a scalable and flexible platform for integration of single- and multiaxis drives on a single chip.

This design comprises FPGA IP, software libraries, and a hardware platform. The design demonstrates DSP Builder and Platform Designer for system integration of IP, bus connections and inclusion of the Nios V/g soft processor. The design includes all software and IP components. The design can be extended and customized to meet your own application needs. The design supports partitioning of algorithms between software running on an integrated processor, and IP performing portions of the motor control algorithm in the FPGA, to accelerate performance.

Additionally, a physical motor and power board have been modeled using DSP Builder tools and included as an IP in the Platform Designer project. This removes the need to have a real motor rig and provides elements to adjust the model to the parameters of other commercial motors and power stages and substitute the IP with a physical setup.

Agilex 7 SoC and HPS

The Agilex 7 HPS implements the second real-time safety channel. For more information about the HPS, refer to the Agilex 7 Hard Processor System Technical Reference Manual.

The design’s software system takes the golden system reference design (GSRD) from RocketBoards.org as the base, which enables the necessary software layers to implement the safety function (HPS channel). You need the meta layer and the hardware collaterals (.rbf and .jic) to get the corresponding hardware and software platforms to run. For more information, refer to the RocketBoards website.

Section Content

Features of the Drive-on-Chip with Functional Safety Design Example for Agilex 7 Devices

About the Safety Concept

Other Drive-on-Chip Design Documents