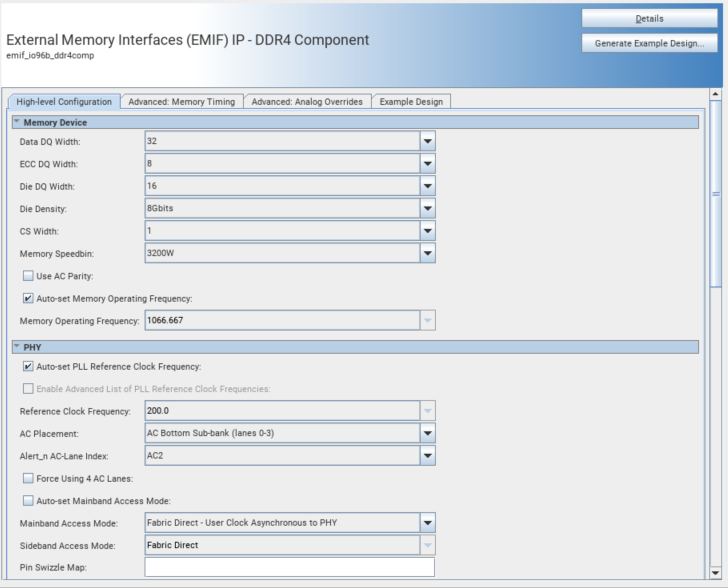

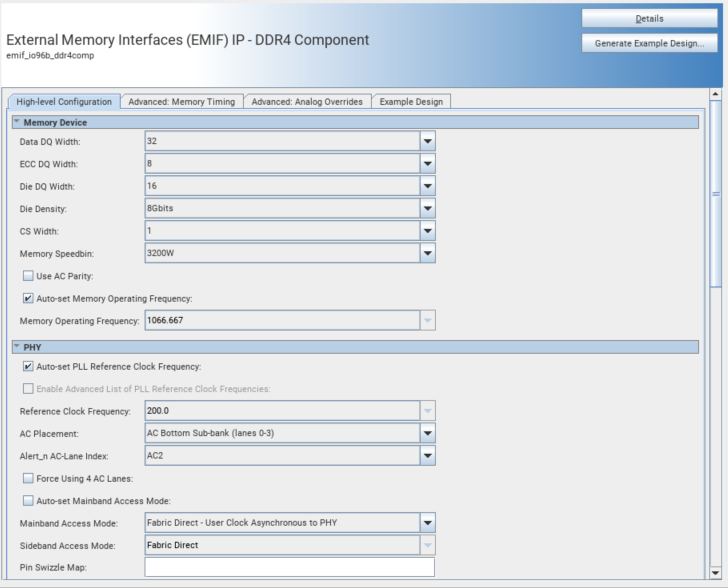

2.2.1. Agilex™ 5 EMIF Parameter Editor Guidelines

This topic provides high-level guidance for parameterizing the tabs in the Agilex™ 5 EMIF IP parameter editor.

| Parameter Editor Tab | Guidelines |

|---|---|

| High Level Parameters | Ensure that you correctly enter the following parameters:

|

| PHY | Allows you to set the following parameters:

|

| Controller Setting | Set the controller parameters according to the desired configuration and behavior for your memory controller:

|

| Memory Timing Setting | Allows you to modify timing parameter settings. |

| Analog Properties | Allows you to modify the termination, drive strength, and VREF settings. |

| Example Design | The Example Design tab lets you select which HDL to use for the top-level files, and which file sets you want the design example to generate:

|

| Performance Monitor | Enable performance monitor on all channels for measuring read/write transaction metrics. |

| Traffic Generator Program | Allows you to specify the traffic pattern that you want to run:

|

Figure 6. External Memory Interfaces IP Parameter Editor

For detailed information on individual parameters, refer to the appropriate protocol-specific chapter in the External Memory Interfaces (EMIF) IP User Guide: Agilex™ 5 FPGAs and SoCs .