Visible to Intel only — GUID: vdn1727204968187

Ixiasoft

Visible to Intel only — GUID: vdn1727204968187

Ixiasoft

5.10. Dual Simplex Support

In cases where the TX IP and RX IP use different parameter settings or the number of TX and RX channels needed differs, you can use a dual simplex (DS) group to maximize your transceiver channel usage.

For a DS group, you may create an independent simplex TX IP (with one or more channels) and an independent simplex RX IP (with one or more channels) and use the Dual Simplex Assignment Editor to fit them into the duplex channel. Refer to the GTS Transceiver Dual Simplex Interfaces User Guide for more information.

- Generate GTS JESD204C TX and RX simplex IP.

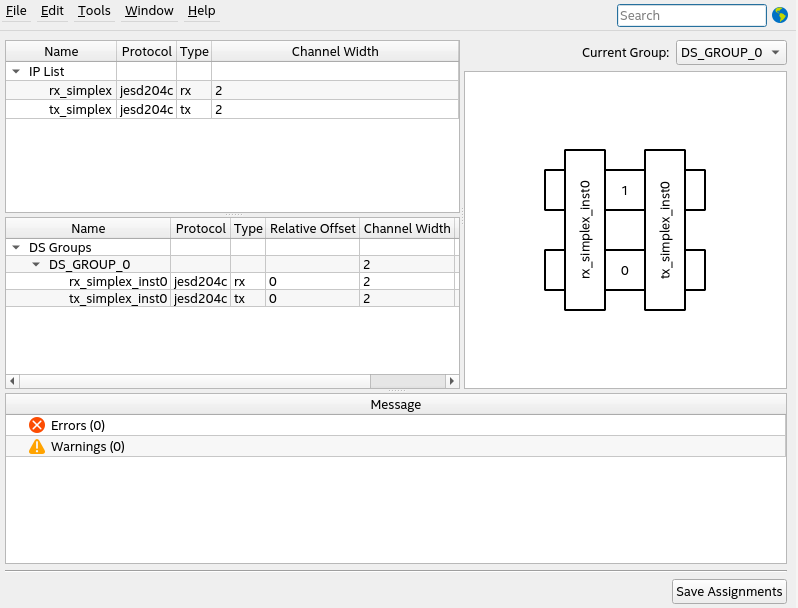

- Provide location of each simplex IP in a DS group relative to the starting channel location in the DS Assignment Editor. To do this, open the Dual Simplex Assignment Editor in Quartus® Prime by selecting Assignments > Dual Simplex (DS) Assignment Editor.

- Assign your individual simplex IPs to a dual simplex (DS) group by right-clicking your IP component under the IP > Click Create Instance in… > Select or create a new DS group.

Figure 23. DS Assignment Editor

The DS Assignment Editor does a quick legality check (protocol level and attribute level) to see if the simplex IPs assigned to a dual simplex group are compatible. If the simplex IPs are not compatible, error messages will be prompted.

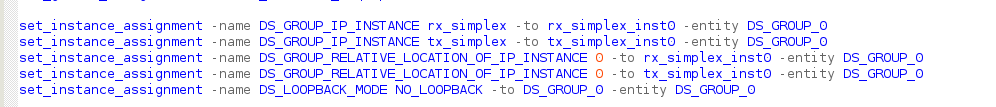

- After assigning simplex IPs to a DS group, save the assignments. When you save the DS group, the QSF assignments are added automatically to the project QSF. For example:

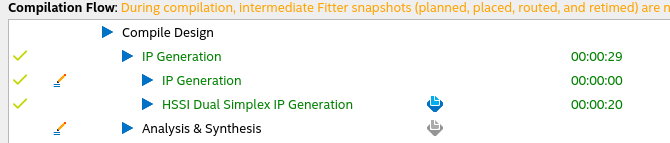

- Run the HSSI Dual Simplex IP Generation in the Compilation Dashboard to obtain a new DS IP:

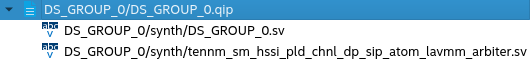

- Connect the generated DS IP to the rest of your design logic:

The Dual Simplex support for the GTS JESD204C IP in current release of the Quartus® Prime software is limited to:

- JESD204C TX IP and JESD204C RX IP only.

- Compilation flow only supported up to Synthesis.

- Simulation only supported for PHY only JESD204C wrapper with up to 4 channels.

- TX IP and RX IP must share the same data rate, PLL/CDR reference clock frequency, and number of lanes per converter device (L).

- Relative Offset in the DS group needs to be 0.

- A DS group only contains one JESD204C TX IP and one JESD204C RX IP