Visible to Intel only — GUID: bwt1685428490972

Ixiasoft

1. 10/100/1000 Ethernet MAC Design Example with 1000BASE-X/SGMII 2XTBI PCS with GTS Transceiver

2. 10/100/1000 Multiport Ethernet MAC Design Example with 1000BASE-X/SGMII PCS and Embedded PMA (LVDS)

3. Triple-Speed Ethernet Intel® FPGA IP Design Example User Guide: Agilex™ 5 FPGAs and SoCs Archives

4. Document Revision History for the Triple-Speed Ethernet Intel® FPGA IP Design Example User Guide: Agilex™ 5 FPGAs and SoCs

Visible to Intel only — GUID: bwt1685428490972

Ixiasoft

1.2.5.1. Test Procedure

After you compile the Triple-Speed Ethernet Intel® FPGA IP design example and configure it on your Agilex™ 5 device, you can use the System Console to program the IP.

To turn on the System Console and test the hardware design example, follow these steps:

Note: You must connect the external loopback module to the QSFP28 port on bank 1A before running the test.

- In the Quartus® Prime Pro Edition software, select Tools > System Debugging Tools>System Console to launch the system console.

- In the Tcl Console pane, type cd hwtest/agx/2xtbi_pma to change directory to <design_example_dir>/hardware_test_design/hwtest/agx/2xtbi_pma.

- Type source basic/basic.tcl.

- Type list_jtag to display a list of JTAG master indexes that are connected to your board.

- Type set_jtag<number_of appropriate_JTAG_master> to select the JTAG master.

- Type source hwtest_main.tcl to run the design example in 10 Mbps, 100 Mbps and 1 Gbps Ethernet speed.

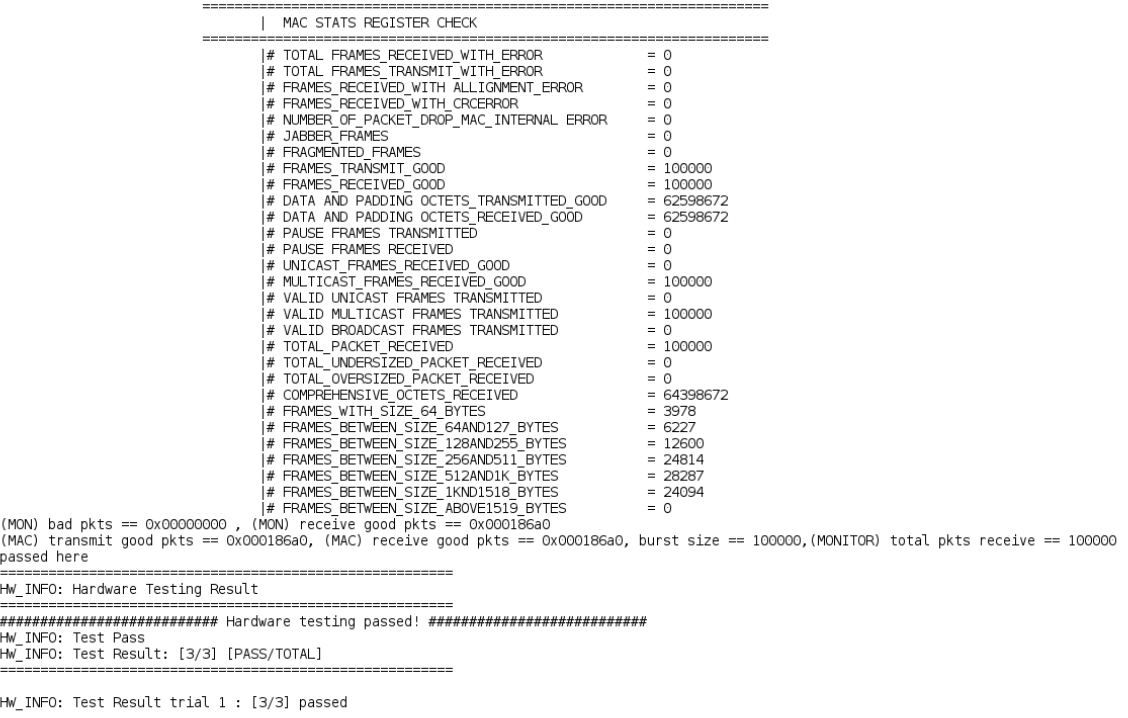

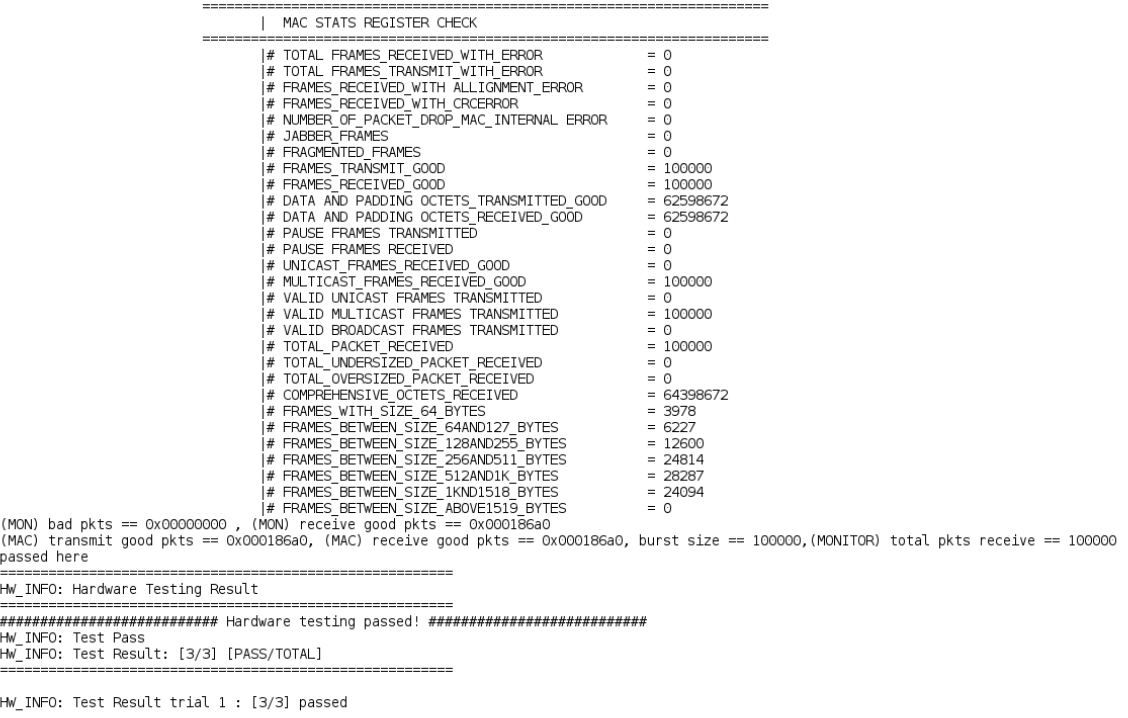

A successful test run displays the following message: