Visible to Intel only — GUID: nbr1710441053381

Ixiasoft

2.1. Parameterizing the HPS Component

2.2. HPS-FPGA Interfaces

2.3. SDRAM

2.4. HPS Clocks, Reset, Power

2.5. I/O Delays

2.6. Pin Mux and Peripherals

2.7. Generating and Compiling the HPS Component

2.8. Using the Address Span Extender Component

2.9. Configuring the Agilex™ 5 Hard Processor System Component Revision History

2.2.1.1. Enable MPU Standby and Event Signals

2.2.1.2. Enable General Purpose Signals

2.2.1.3. Enable Debug APB* Interface

2.2.1.4. Enable System Trace Macrocell (STM) Hardware Events

2.2.1.5. Enable SWJ-DP JTAG Interface

2.2.1.6. Enable FPGA Cross Trigger Interface

2.2.1.7. Enable AMBA* Trace Bus (ATB)

3.1. Simulation Flows

3.2. Running the Simulation of the Design Examples

3.3. Clock and Reset Interface

3.4. FPGA-to-HPS AXI* Subordinate Interface

3.5. FPGA-to-SDRAM AXI* Subordinate Interface

3.6. HPS-to-FPGA AXI* Initiator Interface

3.7. Lightweight HPS-to-FPGA AXI* Initiator Interface

3.8. Simulating the Agilex™ 5 HPS Component Revision History

Visible to Intel only — GUID: nbr1710441053381

Ixiasoft

3.2.1.1. Steps to run the Simulation in Questa* Intel® FPGA Edition

- Install Quartus® Prime Pro Edition software version 23.4 or newer version.

- Set the Quartus® Prime installation directory as: $QUARTUS_ROOTDIR.

- In Terminal, launch the Questa* Intel® FPGA Edition with the following command:

vsim -mvchome $QUARTUS_ROOTDIR/../ip/altera/ \ mentor_vip_ae/common &

Note: The vsim command is used to invoke the VSIM simulator, the mvchome path must point to the correct installation directory. - In the QuestaSim* Transcript window, execute the do run.do script to start the simulation.

Questa> do run.do

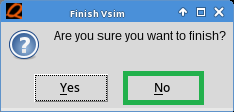

- Once the simulation is completed, select “No” when you see the prompt to close the simulator.

Figure 46. Close Confirmation Dialog Box

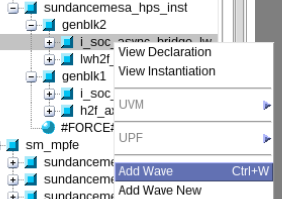

- Observe the transcript window messages and check the “Wave” window to see the signals’ waveforms. You may add in more waveform by performing a right-click on a signal and select “Add Wave”, and then click on the restart button to generate the waveform of the newly added signal.

Figure 47. Add Wave Drop-Down Menu

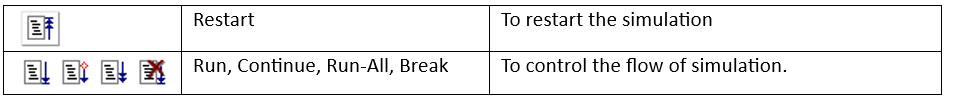

Figure 48. Restart Simulation

Figure 48. Restart Simulation

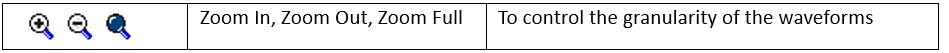

- The “wave” window allows you to check the waveforms of the selected signals. You may use the zoom control buttons to see the details of the waveforms.

Figure 49. Waveform Granularity Controls

Figure 50. Waveform OutputNote: The master_test_program.sv, run.do, wave.do and all project files included in the compressed package are for the example design provided. Any new changes to the RTL, parameters, project setting, configuration and project naming requires a modification to the master_test_program.sv, run.do file, and wave.do file.

Figure 50. Waveform OutputNote: The master_test_program.sv, run.do, wave.do and all project files included in the compressed package are for the example design provided. Any new changes to the RTL, parameters, project setting, configuration and project naming requires a modification to the master_test_program.sv, run.do file, and wave.do file.For more information about how to customize a new design, please refer to Mentor Graphics* : Mentor VIP - Intel FPGA Edition AMBA* AXI* 3 and AXI* 4 User Guide