Visible to Intel only — GUID: vij1675787564337

Ixiasoft

Visible to Intel only — GUID: vij1675787564337

Ixiasoft

3.6.2. Recommended Placement Order for NoC Elements in Interface Planner

For best results, place NoC-related elements in the following order, starting with the IP containing the NoC targets.

If your design uses HPS, perform the following step:

- Click the Autoplace Fixed button to place any elements that have only one legal location. Repeat clicking the Autoplace Fixed button to place directly connected elements until Interface Planner displays the message 'No elements found with only 1 legal location’.

If your design uses HPS and any external memory interfaces associated with the HPS remain unplaced after the previous step, perform the following steps:

- For each HPS external memory, expand the IP in the Design Element pane and locate the RZQ pin, the element whose name ends in …oct_rzqin~CLUSTER.

- Right-click on this element and click Generate Legal Locations for Selected Elements. The Interface Planner may display multiple legal locations, depending on prior placements.

- Select the RZQ pin for the I/O bank that you want to implement your external memory interface. Refer to the pinout tables for your device to identify the RZQ pin associated with the target bank. Note that you must place external memory interfaces for HPS in the I/O bank or banks adjacent to the HPS. Right-click on the desired pin location from the list of legal locations and click Place at Selected.

- Click the Autoplace Fixed button to place directly connected elements. Repeat clicking the Autoplace Fixed button until Interface Planner displays the message ‘No elements found with only 1 legal location’. The placement of this IP block is complete, and you can proceed to the next IP.

For each HBM2e IP in your design, perform the following steps:

- Expand the IP in the Design Element pane and locate the HBM controller, the element whose name ends in “…|xhmbc."

- Right-click on this element and click Generate Legal Locations for Selected Elements. The Interface Planner may display one or two legal locations, depending on prior placements.

- Select the HBM2e location along the top edge or bottom edge of the die based on your design requirements. Right-click on the desired location from the list of legal locations and click Place at Selected.

- Click the Autoplace Fixed button to place directly connected elements. Repeat pressing the Autoplace Fixed button until Interface Planner displays the message ‘No elements found with only 1 legal location’. At this point, the placement of the IP block is complete, and you can proceed to the next IP.

For each external memory interface in your design, perform the following steps:

- Expand the IP in the Design Element pane and locate the RZQ pin, the element whose name ends in “…oct_rzqin~CLUSTER."

- Right-click on this element and click Generate Legal Locations for Selected Elements. The Interface Planner may display multiple legal locations, depending on prior placements.

- Select the RZQ pin for the I/O bank that you want to implement your external memory interface. Refer to the pinout tables for your device to identify the RZQ pin associated with the target bank. Right-click on the desired pin location from the list of legal locations and select Place at Selected.

- Click the Autoplace Fixed button to place directly connected elements. Repeat pressing the Autoplace Fixed button until Interface Planner displays the message ‘No elements found with only 1 legal location’. At this point, the placement of this IP block is complete, and you can proceed to the next IP.

After placing all the IP containing the NoC targets, Interface Planner also places the NoC Clock Control IP containing the NoC PLL and the NoC SSM. These placements are based on the group assignments that you make in the NoC Assignment Editor.

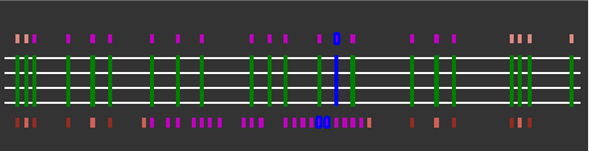

Proceed with placing the NoC initiators by switching to the NoC View. This view shows the target interface bridges that you have placed. As you place each initiator, Interface Planner highlights the targets connected to the initiator, as well as the switches and horizontal links that form the connection. When placing each initiator, consider the targets that are accessed by that initiator.

If you click on the NoC switches represented by the green vertical bars, Interface Planner displays the initiators and targets that connect directly to that switch.

If you place the initiator such that it only uses the vertical switch to connect to its target, its traffic does not use the horizontal links. That placement avoids the traffic causing congestion on the links that are in use for other initiator-to-target connections. Place the initiator close to the targets that require low-latency or high-bandwidth accesses. Since HBM2e channels are functionally interchangeable, you can also shorten communication paths across the NoC by choosing HBM2e channels that are close to your ideal initiator location.

External Memory Interfaces and other GPIO functions that bypass the NOC can conflict with initiator interface bridges placement, as GPIO-B Bypass Mode and Initiators describes. Depending on design requirements, you can place these I/O functions that bypass the NoC before or after placing the NoC initiator interfaces. Placing I/O functions first gives greater flexibility to their placement, while restricting which initiator locations you can use. Placing NoC initiator interface bridges first allows optimal initiator placement, while restricting which I/O locations are available.

Other interfaces, such as transceivers, have no direct interaction with the hard memory NoC. Therefore, you can place such interfaces before or after the NoC.