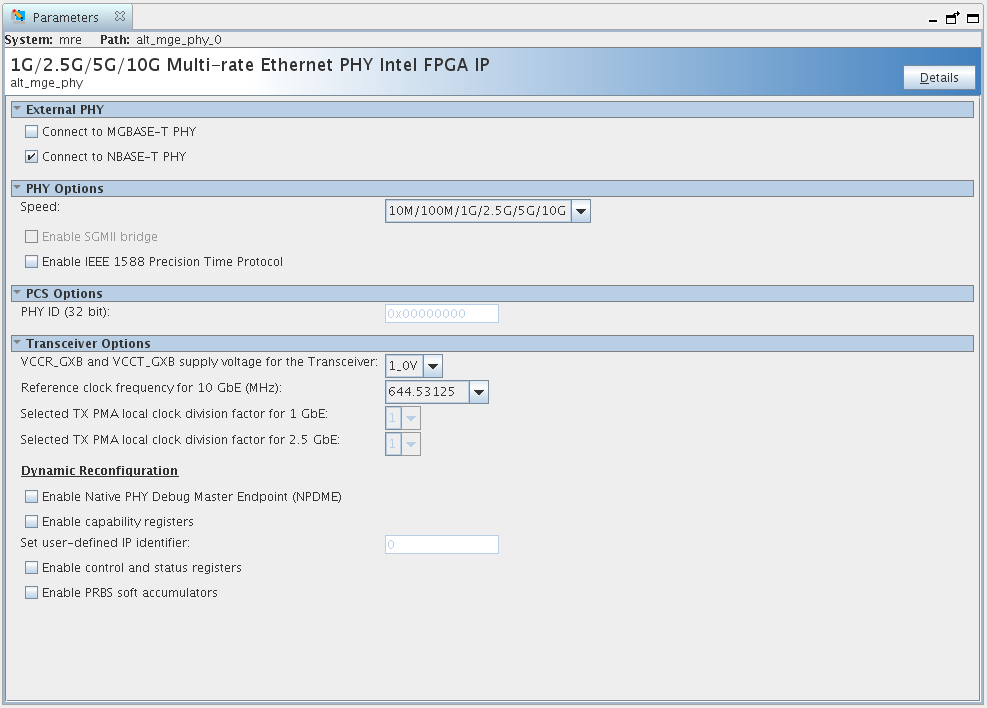

3. Parameter Settings

| Parameter | Options | Description |

|---|---|---|

| External PHY | ||

| Connect to MGBASE-T PHY | On, Off | Select this option when the external PHY is MGBASE-T compatible. This parameter is enabled for 2.5G, 1G/2.5G, and 1G/2.5G/10G (MGBASE-T) modes. |

| Connect to NBASE-T PHY | On, Off | Select this option when the external PHY is NBASE-T compatible. This parameter is enabled for 10M/100M/1G/2.5G/5G/10G (USXGMII) modes. |

| PHY Options | ||

| Speed | 2.5G 1G/2.5G 1G/2.5G/10G 10M/100M/1G/2.5G/5G/10G |

The operating speed of the PHY. |

| Enable SGMII bridge | On, Off | Select this parameter to enable SGMII 10-Mbps/100-Mbps/1-Gbps. You can enable this parameter for 1G/2.5G, and 1G/2.5G/10G (MGBASE-T) modes. |

| Enable IEEE 1588 Precision Time Protocol | On, Off | Select this parameter for the PHY to provide latency information to the MAC. The MAC requires this information if it enables the IEEE 1588v2 feature. You can enable this parameter for 2.5G, 1G/2.5G, 1G/2.5G/10G (MGBASE-T), and 10M/100M/1G/2.5G/5G/10G (USXGMII) modes provided that the SGMII bridge is disabled in 1G/2.5G and 1G/2.5G/10G (MGBASE-T) modes. |

| PCS Options | ||

| PHY ID (32 bit) | 32-bit value | An optional 32-bit unique identifier:

The default value is 0x00000000. |

| Transceiver Options | ||

| VCCR_GXB and VCCT_GXB supply voltage for the transceivers | 1.0 V, 1.1 V | This parameter specifies the VCCR_GXB and VCCT_GXB transceiver supply voltage. The default setting is 1.0 V. Use 1.1 V setting if the bank contains transceivers running at 15 Gbps or faster. |

| Reference clock frequency for 10 GbE (MHz) | 322.265625, 644.53125 | Specify the frequency of the reference clock for 10GbE. This option is only available for 1G/2.5G/10G and 10M/100M/1G/2.5G/5G/10G (USXGMII) speed modes. |

| Selected TX PMA local clock division factor for 1 GbE | 1, 2, 4, 8 | Select the TX local clock division factor for transceiver. The selection is used for 1G Ethernet. |

| Selected TX PMA local clock division factor for 2.5 GbE | 1, 2 | Select the TX local clock division factor for transceiver. The selection is used for 2.5G Ethernet. |

| Dynamic Reconfiguration | ||

| Enable Native PHY Debug Master Endpoint (NPDME) | On, Off | When enabled, the Native PHY includes an embedded Native PHY Debug Master Endpoint (NPDME) that connects internally Avalon® -MM slave interface. The NPDME can access the reconfiguration space of the transceiver. It can perform certain test and debug functions via JTAG using the System Console. |

| Enable capability registers | On, Off | Enables capability registers. These registers provide high-level information about the transceiver channel/PLL configuration. |

| Set user-defined IP identifier | User-specified | Sets a user-defined numeric identifier that can be read from the user_identifier offset when the capability registers are enabled. |

| Enable control and status registers | On, Off | Enables soft registers for reading status signals and writing control signals on the PHY /PLL interface through the NPDME or reconfiguration interface. |

| Enable PRBS soft accumulators | On, Off | Enables soft logic to perform PRBS bit and error accumulation when using the hard PRBS generator and checker. |