Visible to Intel only — GUID: xbg1615854170190

Ixiasoft

Visible to Intel only — GUID: xbg1615854170190

Ixiasoft

6.4. Instantiating the F-Tile Reference and System PLL Clocks Intel® FPGA IP

The F-Tile Reference and System PLL Clocks Intel® FPGA IP is required for F-tile PMA/FEC Direct PHY designs. You must instantiate and connect this IP for simulation and compilation.

This design requires the following for the F-Tile Reference and System PLL Clocks Intel® FPGA IP:

- System PLL mode and reference clock source for one system PLL that clocks the datapath.

- Reference clock source for FGT PMA. Share or separate the reference clock source for system PLL and FGT PMA. This example shares the reference clock.

To specify the system PLL mode and reference clock source for one system PLL:

- In the IP Catalog search field, type f-tile Reference, and double-click the F-Tile Reference and System PLL Clocks Intel® FPGA IP under Transceiver PHY.

- On the System PLL #0 tab, specify the following:

Table 107. System PLL #0 Options Parameter Parameter Value Mode of system PLL Select ETHERNET_FREQ_830_156. This configures the system PLL input frequency to 156.25 MHz and output frequency to 830.078125 MHz (must match system PLL frequency in F-Tile PMA/FEC Direct PHY Intel® FPGA IP). Refclk source RefClk #0. Selects the reference clock source for system PLL. RefClk #0 for FGT PMA On - Under RefClk, specify the following options:

Table 108. RefClk Options Parameter Parameter Value Enable RefClk #0 for FGT PMA On. This reference clock is shared between system PLL #0 and FGT PMA RefClk source RefClk #0. 156.25 MHz (same as reference clock frequency for F-Tile PMA/FEC Direct PHY Intel® FPGA IP).

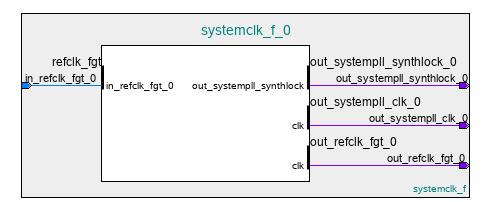

The following figures shows the block symbol and available ports for F-Tile Reference and System PLL Clocks Intel® FPGA IP in this example