Quartus® Prime Pro Edition User Guide: Third-party Simulation

A newer version of this document is available. Customers should click here to go to the newest version.

Visible to Intel only — GUID: qvu1701121056974

Ixiasoft

Visible to Intel only — GUID: qvu1701121056974

Ixiasoft

5.2. Generating Simulator Setup Script Templates

Follow these steps to generate the vendor-specific simulator setup script templates for the IP modules in your design. You can then customize these templates for your specific simulation goals.

- To compile your design, click Processing > Start Compilation. The Messages window indicates when compilation is complete.

- Click Tools > Generate Simulator Setup Script for IP.

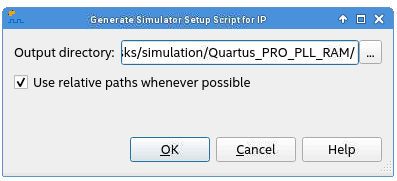

- Retain the default settings for the Output directory and also the Use relative paths whenever possible option.

- To generate the setup script templates and vendor-specific sub-folders, including xcelium/ and common/ in the specified output directory, click OK.

Figure 18. Generate Simulator Setup Script for IP Dialog Box