Visible to Intel only — GUID: mtr1422491957790

Ixiasoft

Visible to Intel only — GUID: mtr1422491957790

Ixiasoft

3.3.9. Static Timing Analysis

| GUI Feature | AMD* Xilinx* Vivado* Software | Intel® Quartus® Prime Pro Edition Software |

|---|---|---|

| Static Timing Analysis | Report Timing | Timing Analyzer |

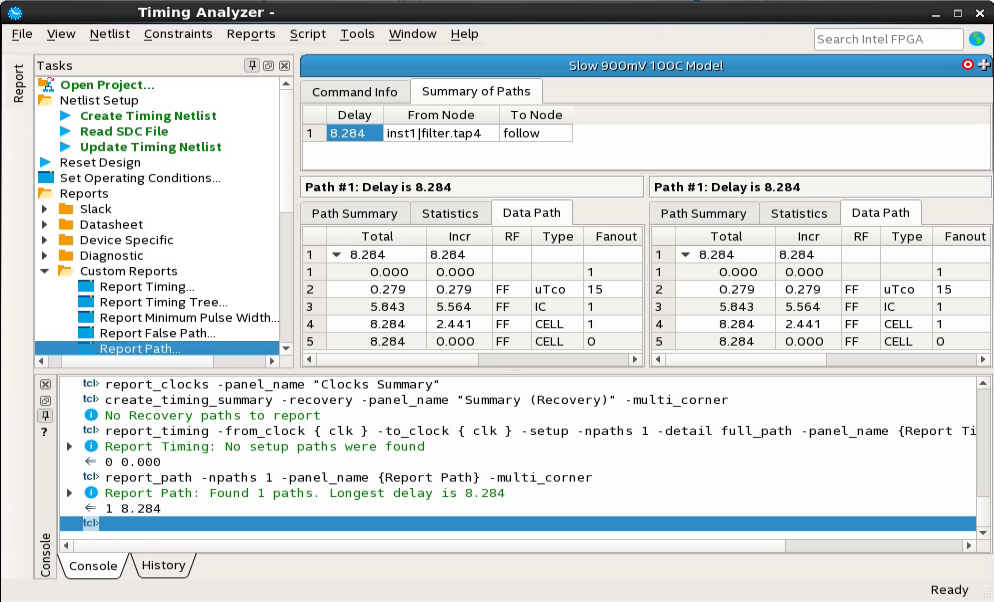

The Intel® FPGA Timing Analyzer is an easy-to-use, second-generation, ASIC-strength static timing analyzer that supports the industry-standard Synopsys* Design Constraints (SDC) format.

The major difference between performing timing analysis with the Report Timing Summary in Vivado* and the Intel® FPGA Timing Analyzer is that in the Vivado* software, a change in timing constraint triggers a recompile. In contrast, the Timing Analyzer GUI allows you to experiment with timing constraints and timing model without recompiling.

Access

Static timing analysis with the Timing Analyzer is part of the full compilation flow, but you can also run the module separately.

To run the Timing Analyzer over a post-fit netlist, click Processing > Start > Start Timing Analyzer .

To open the Timing Analyzer GUI, click Tools > Timing Analyzer .