Multi Channel DMA Intel® FPGA IP for PCI Express* Design Example User Guide

A newer version of this document is available. Customers should click here to go to the newest version.

Visible to Intel only — GUID: cbn1590190547504

Ixiasoft

Visible to Intel only — GUID: cbn1590190547504

Ixiasoft

2.5. Avalon-ST Device-side Packet Loopback

This design example performs H2D and D2H multi channel DMA via device-side Avalon-ST streaming interface. With device-side packet loopback, Host to Device (H2D) data stream is loop backed to the Host (D2H) through an external FIFO.

For H2D streaming, Multi Channel DMA sends the data to Avalon-ST loopback FIFOs via four Avalon-ST Source ports. For D2H streaming, Multi Channel DMA receives the data from Avalon-ST loopback FIFOs via Avalon-ST Sink ports.

In this device-side loopback example, the Host first sets up memory locations within the Host memory. Data from the Host memory is then sent to the device-side memory by the Multi Channel DMA for PCI Express IP via H2D DMA operations. Finally, the IP loops this data back to the Host memory using D2H DMA operations.

In addition, the design example enables Avalon-MM PIO master which bypasses the DMA path. It allows application to perform single, non-bursting register read/write operation with on-chip memory block.

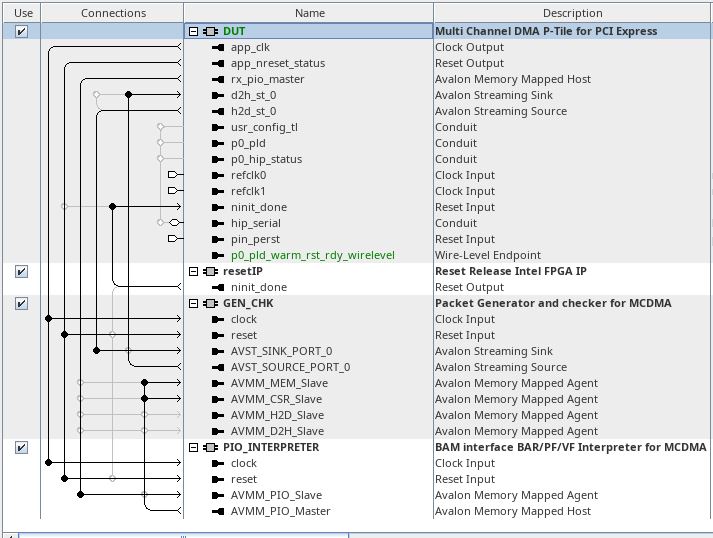

- resetIP – Reset Release IP that holds the Multi Channel DMA in reset until the entire FPGA fabric enters user mode

- GEN_CHK - Packet Generator and Checker for MCDMA. It interfaces with DUT Avalon Streaming H2D/D2H interfaces (h2d_st_0, d2h_st_0) for DMA operation. DUT AVMM PIO Master (rx_pio_master) performs read and write operations to the CSR and On-chip memory.

- PIO_INTERPRETER - This maps DUT AVMM PIO Master address width to AVMM Slave side address based on its parameter setting such as MAP_PF, MAP_VF, and MAP_BAR.

- PIO test: -o

- DMA test: -i (performance loopback operation where the Tx and Rx are run in two different threads), -v (enable data validation, which will perform a data integrity check).

- -i without -v flag displays the throughput per channel

For a description of which driver(s) to use with this design example, refer to Driver Support.