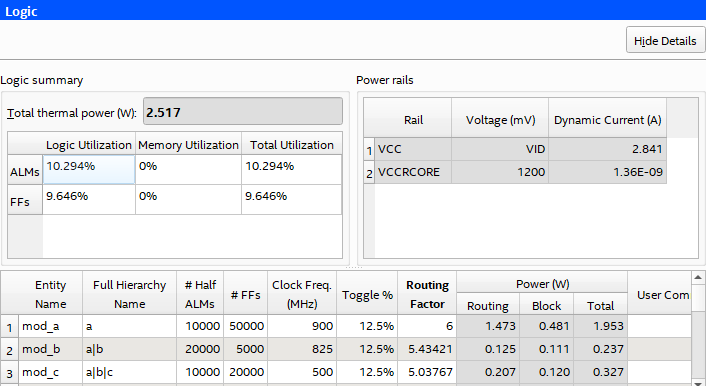

5.4. Intel® FPGA PTC - Logic Page

| Column Heading | Description | |

|---|---|---|

| Entity Name | Specify a name for each entity of the design. This is an optional entry. |

|

| Full Hierarchy Name | Specify the hierarchical path relevant to this entry. This is an optional entry. When entering levels of hierarchy, the pipe character (|) denotes a level of hierarchy. (Instance paths may, optionally, begin with a leading pipe character; but regardless of whether a leading pipe is there or not, paths are treated the same.) | |

| #Half ALMs | Enter twice the number of Adaptive Logic Modules (ALMs) used in your design, which you can find in the Compilation Report, by selecting . For power estimation purposes, the number of ALMs used in your design is the sum of the following values in the Compilation Report:

The adjustment for power estimation is necessary because some unused ALMs may still consume power due to Fitter optimizations. For more information, refer to Calculating Register Utilization.

Note: This field can also accept a percentage (for example, 10%) as an input, which is used to calculate the number of half ALMs. The "%" character informs PTC to appropriately compute and apply the resource count as an integer.

|

|

| # FFs | Enter the number of Primary logic registers, plus Secondary logic registers, plus the number of registers reported as Register control circuitry for power estimation, all of which you can find in the Compilation Report, by selecting . The Register control circuitry for power estimation adjustment is necessary because some unused registers may still consume power due to fitter optimizations. Clock routing power associated with flipflops is calculated separately on the Clock page of the Intel® FPGA PTC.

Note: This field can also accept a percentage (for example, 10%) as an input, which is used to calculate the number of flipflops,

|

|

| Clock Freq (MHz) | Enter a clock frequency (in MHz). This value is limited by the maximum frequency specification for the device family. For Intel® Stratix® 10 devices, when you import a design from the Intel® Quartus® Prime software, some imported half ALMs and flipflops may have a clock frequency of 0 MHz; this can occur for one of two reasons:

It is possible that due to the floating point precision used in the tool, the frequency reported may differ slightly from what is reported in the Timing Analyzer. |

|

| Toggle % | Enter the average percentage of clock cycles when the block output signals change values. Toggle percentage is multiplied by clock frequency to determine the number of transitions per second. For example, 100 MHz frequency with a 12.5% toggle rate, means that each LUT or flipflop output toggles 12.5 million times per second (100MHz × 12.5%). The toggle percentage ranges from 0 to 100%. Typically, the toggle percentage is 12.5%, which is the toggle percentage of a 16-bit counter. Most logic only toggles infrequently; therefore, toggle rates of less than 50% are more realistic. To ensure you do not underestimate the toggle percentage, use a realistic toggle percentage obtained through simulation. For example, a T flipflop (TFF) with its input tied to VCC has a toggle rate of 100% because its output is changing logic state on every clock cycle. Refer to the 4-Bit Counter Example below for a more detailed analysis. For any rows containing flipflops, toggle percentage cannot exceed 100%. A small portion of ALMs in a design may experience glitching that results in toggle percentage exceeding 100% for such ALMs. Enter such ALMs into a separate row with # FFs set to 0. For Intel® Stratix® 10 devices in the Intel® FPGA PTC, toggle percentage cannot exceed 100% in any rows containing flipflops. |

|

| Routing Factor | Indicates the extent of the routing power of the outputs. Characteristics that have a large power impact and are captured by this factor include the following:

The default value for this field is typical; the actual value varies between blocks in your design, and depends on the placement of your design. For most accurate results, you should import this value from the Intel® Quartus® Prime software after compiling your design, because the Intel® Quartus® Prime software has access to detailed placement and routing information. In the absence of an Intel® Quartus® Prime design, higher values generally correspond to signals that span large distances on the FPGA and fanout to many destinations, while lower values correspond to more localized signals. You can change this field from its default value to explore possible variations in power consumption depending on block placement. When changing this value, keep in mind that typical designs rarely use extreme values, and only for a small subset of the design. |

|

| Power (W) | Routing | Indicates the power dissipation due to estimated routing (in W). Routing power depends on placement and routing, which is a function of design complexity. The values shown are representative of routing power based on observed behavior across more than 100 real-world designs. Use the Intel® Quartus® Prime Power Analyzer for accurate analysis based on the exact routing used in your design.

Note: Only routing power used for Logic resources is included here.

|

| Block | Indicates the power dissipation due to internal toggling of the ALMs and registers (in W). Logic block power is a combination of the function implemented and the relative toggle rates of the various inputs. The Intel® FPGA PTC uses an estimate based on observed behavior across more than 100 real-world designs. Use the Intel® Quartus® Prime Power Analyzer for accurate analysis based on the exact synthesis of your design. |

|

| Total | Indicates the estimated power (in W), based on information entered into the Intel® FPGA PTC. It is equal to the sum of routing power and block power. |

|

| User Comment | Enter any comments. This is an optional entry. |

|

Calculating ALM Utilization

ALM utilization reported by the Intel® FPGA PTC may differ from utilization reported by the Intel® Quartus® Prime Fitter.

The Fitter counts resources used by design logic, and reports logic utilization to help you understand whether the device has more available room in which to fit additional logic. The Intel® FPGA PTC counts resources that require power in the physical silicon implementation.

From a power perspective, the estimate of total ALM utilization includes both the ALMs used by the design logic and other resources not counted by the Fitter that also consume power. The ALMs adjustment for power estimation value represents the powered resources not counted by the Fitter.

As an example, for a circuit with two flipflops placed in two different ALM locations, the Fitter reports one ALM of logic utilization—because the flipflops could be packed more densely if the chip was more fully utilized. But from the power perspective, the utilization is two, because two physical ALMs are consumed and powered on the chip. Because the Intel® FPGA PTC tracks the number of half ALMs, you should enter 4 half ALMs into the #Half ALMs column.

The following equation represents the calculation of the total number of half-ALMs consuming power:

# Half ALMs = (ALMs used for LUT logic and register circuitry + ALMs used for LUT logic + ALMs used for register circuitry + ALMs adjustment for power estimation) * 2

Calculating Register Utilization

The following equation represents the calculation of the total number of registers consuming power:

Total ALM Registers for power estimation = Primary logic registers + Secondary logic registers + Register control circuitry for power estimation

This example illustrates the above equation: The primary logic registers and secondary logic registers account for the ALM registers used by the design, and are reported by the Fitter.

The register control circuitry for power estimation is an adjustment that accounts for the ALM registers bypassed in the design. When Fitter timing optimizations result in a register being retimed from an ALM register location into a Hyper-Register location, the ALM register location is configured to be in “bypass mode," which still consumes power.

Calculating Toggle %

The following example illustrates the calculation of toggle percentage.

The cout0 output of the first TFF has a toggle percentage of 100% because the signal toggles on every clock cycle. The toggle percentage for the cout1 output of the second TFF is 50% because the output toggles every two clock cycles. Similarly, the toggle percentage for the cout2 and cout3 outputs are 25% and 12.5%, respectively. Therefore, the average toggle percentage for this 4-bit counter is (100 + 50 + 25 + 12.5)/4 = 46.875%.

For more information about logic block configurations, refer to the Intel Agilex® 7 Logic Array Blocks and Adaptive Logic Modules User Guide.