Visible to Intel only — GUID: dsc1635787312729

Ixiasoft

1. Answers to Top FAQs

2. Overview of the Intel® FPGA Power and Thermal Calculator

3. Estimating Power Consumption with the Intel® FPGA Power and Thermal Calculator

4. Intel® FPGA Power and Thermal Calculator Graphical User Interface

5. Intel® FPGA Power and Thermal Calculator Pages

6. Factors Affecting the Accuracy of the Intel® FPGA PTC

7. Intel® FPGA Power and Thermal Calculator User Guide Archive

8. Document Revision History for the Intel® FPGA Power and Thermal Calculator User Guide

A. Measuring Static Power

4.2.2.1. Using Design Hierarchies in the Intel® FPGA Power and Thermal Calculator

4.2.2.2. Entering Hierarchy Information Into the Intel® FPGA PTC

4.2.2.3. Exporting, Importing, Duplicating, Renaming, and Deleting Hierarchies in the Intel® FPGA PTC

4.2.2.4. Bulk Editing Hierarchies in the Intel FPGA PTC

5.1. Intel® FPGA PTC - Power Summary/Navigation

5.2. Intel® FPGA PTC - Common Page Elements

5.3. Intel® FPGA PTC - Main Page

5.4. Intel® FPGA PTC - Logic Page

5.5. Intel® FPGA PTC - RAM Page

5.6. Intel® FPGA PTC - DSP Page

5.7. Intel® FPGA PTC - Clock Page

5.8. Intel® FPGA PTC - PLL Page

5.9. Intel® FPGA PTC - I/O Page

5.10. Intel® FPGA PTC - Transceiver Page

5.11. Intel® FPGA PTC - HPS Page

5.12. Intel® FPGA PTC - Crypto Page

5.13. Intel FPGA PTC - NOC Page

5.14. Intel® FPGA PTC - HBM Page

5.15. Intel® FPGA PTC - Thermal Page

5.16. Intel® FPGA PTC - Report Page

Visible to Intel only — GUID: dsc1635787312729

Ixiasoft

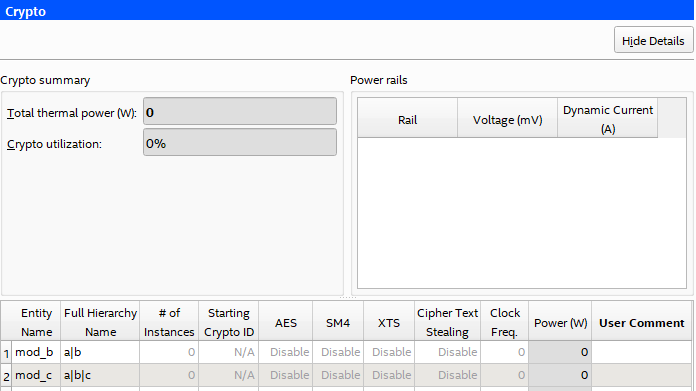

5.12. Intel® FPGA PTC - Crypto Page

The Crypto data entry page is only for Intel Agilex® 7 devices with crypto blocks. Only a subset of Intel Agilex® 7 devices have crypto blocks, consisting of hardened logic that can perform encryption and decryption functions. The Crypto data entry page of the Intel® FPGA Power and Thermal Calculator (PTC) allows you to configure crypto blocks for Intel Agilex® 7 devices equipped with those blocks, and to obtain power estimates for crypto use.

Note: Not all Intel Agilex® 7 devices have crypto blocks. Parameter entry is unavailable if the currently selected device does not have crypto blocks.

Figure 49. Crypto Page of the Intel® FPGA PTC

Crypto Summary

| Column Heading | Description |

|---|---|

| Total thermal power (W) | Reports the total thermal power of the crypto blocks in watts (W). |

| Crypto utilization | Reports the percentage utilization of the crypto block resources. |

Crypto Page Information

| Column Heading | Description |

|---|---|

| Entity Name | Specify a name for each entity in the design. This is an optional value. |

| Full Hierarchy Name | Specify the hierarchical path relevant to this entry. This is an optional entry. When entering levels of hierarchy, the pipe character (|) denotes a level of hierarchy. |

| # of Instances | Enter the number of crypto block instances with the same parameters. |

| Crypto ID | Specify placement information for thermal modeling. This field is available only when # of Instances is set to 1. |

| AES | Specify whether to enable or disable Advanced Encryption Standard (AES) for the crypto block. |

| SM4 | Specify whether to enable or disable SM4 (a block cipher used to encrypt and decrypt data) for the crypto block. |

| XTS | Specify whether to enable or disable XEX Tweakable Block Ciphertext Stealing (a block cipher mode of operation, abbreviated as XTS) for the crypto block. |

| Cipher Text Stealing | Specify whether to enable or disable Cipher Text Stealing (CTS) for the crypto block. CTS can be enabled only if XTS is also enabled. |

| Clock Freq (MHz) | Specify the frequency of the clock, in MHz. |

| Total Power (W) | Indicates the total estimated power for this row, in watts (W). |

| User Comment | Enter any comments. This is an optional entry. |

Related Information