Visible to Intel only — GUID: eis1414471362957

Ixiasoft

1. Intel® MAX® 10 Embedded Memory Overview

2. Intel® MAX® 10 Embedded Memory Architecture and Features

3. Intel® MAX® 10 Embedded Memory Design Consideration

4. RAM: 1-Port IP Core References

5. RAM: 2-PORT IP Core References

6. ROM: 1-PORT IP Core References

7. ROM: 2-PORT IP Core References

8. FIFO IP Core References

9. Shift Register (RAM-based) IP Core References

10. ALTMEMMULT IP Core References

11. Document Revision History for the Intel® MAX® 10 Embedded Memory User Guide

Visible to Intel only — GUID: eis1414471362957

Ixiasoft

8.3. FIFO Functional Timing Requirements

The wrreq signal is ignored (when FIFO is full) if you enable the overflow protection circuitry in the FIFO Intel® FPGA IP parameter editor, or set the OVERFLOW_CHECKING parameter to ON. The rdreq signal is ignored (when FIFO is empty) if you enable the underflow protection circuitry in the FIFO Intel® FPGA IP core interface, or set the UNDERFLOW_CHECKING parameter to ON.

If the protection circuitry is not enabled, you must meet the following functional timing requirements:

| DCFIFO | SCFIFO |

|---|---|

| Deassert the wrreq signal in the same clock cycle when the wrfull signal is asserted. | Deassert the wrreq signal in the same clock cycle when the full signal is asserted. |

| Deassert the rdreq signal in the same clock cycle when the rdempty signal is asserted. You must observe these requirements regardless of expected behavior based on wrclk and rdclk frequencies. | Deassert the rdreq signal in the same clock cycle when the empty signal is asserted. |

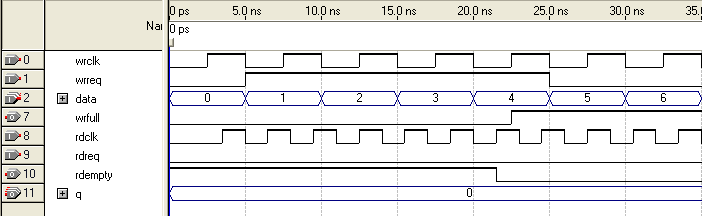

Figure 26. Functional Timing for the wrreq Signal and the wrfull SignalThis figure shows the behavior for the wrreq and the wrfull signals.

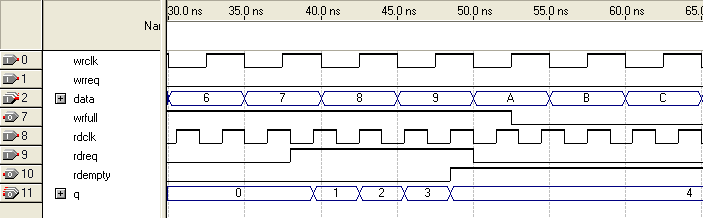

Figure 27. Functional Timing for the rdreq Signal and the rdempty SignalThis figure shows the behavior for the rdreq the rdempty signals.

The required functional timing for the DCFIFO as described previously is also applied to the SCFIFO. The difference between the two modes is that for the SCFIFO, the wrreq signal must meet the functional timing requirement based on the full signal and the rdreq signal must meet the functional timing requirement based on the empty signal.