Visible to Intel only — GUID: ijw1661937234333

Ixiasoft

Visible to Intel only — GUID: ijw1661937234333

Ixiasoft

36.3.1. Coefficient Selection

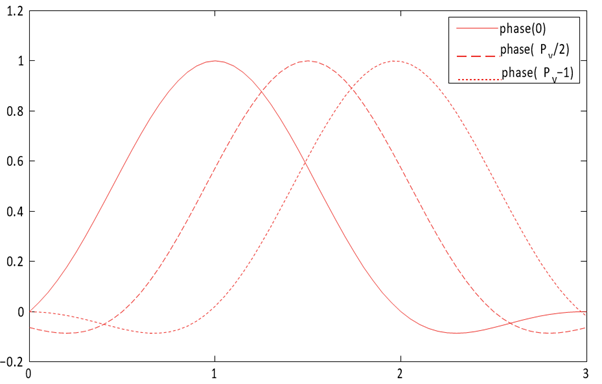

Generally, the set of coefficients that the IP writes to filter phase 0 yield a low-pass filter, with most weight in generating the output pixel value given to the pixel value in tap . The function is centered at tap . The coefficients the IP writes to the other phases are then just phase-shifted versions of this function (hence the name phase for each coefficient address), with the function centered at a point that is shifted by 1/ num_of_pixels of a pixel with every subsequent phase.

The Lanczos function is a common function that defines scaling coefficients. The Lanczos function is a base sinc function, with the primary lobe of a sinc function used as a window function to preserve a given number of lobes of the base sinc. The number of lobes is generally appended to Lanczos when referring to a specific variant of the function, so a Lanczos function where two lobes are preserved is referred to as Lanczos2. In the case where N lobes are preserved, the LanczosN function is defined as:

When using LanczosN coefficients, Intel recommends configuring the scaler filters with the following numbers of taps for the upscale and downscale cases:

- Upscale: 2 × N

- Downscale:

The number of lobes in the Lanczos function affects the frequency response of the filter and, as a result, the quality of the image produced. Generally, Lanczos functions with lower numbers of lobes give a softer frequency response and a resulting image with more blur on the edges, but with less risk of ringing artifacts in the areas immediately around the edges. Conversely, Lanczos functions with higher numbers of lobes give sharper edges but introduce more ringing artifacts. Lanczos2 is a good compromise between minimizing blur and minimizing ringing, but you can experiment with Lanczos3 or Lanczos4 to make your own judgment. The higher the number of lobes, the more filter taps (and therefore FPGA device resources) the design requires to implement the filter correctly. You should experiment with Lanczos1 coefficients for large downscales.