Visible to Intel only — GUID: lro1431976733141

Ixiasoft

Visible to Intel only — GUID: lro1431976733141

Ixiasoft

6.5. Building the FPH2 Example Hardware

To instantiate the FPH2 component in your system, in Platform Designer, locate the Floating Point Hardware 2 component in the Project area of the Component Library. The FPH2 component is located under the “Embedded Processors” group in the Component Library.

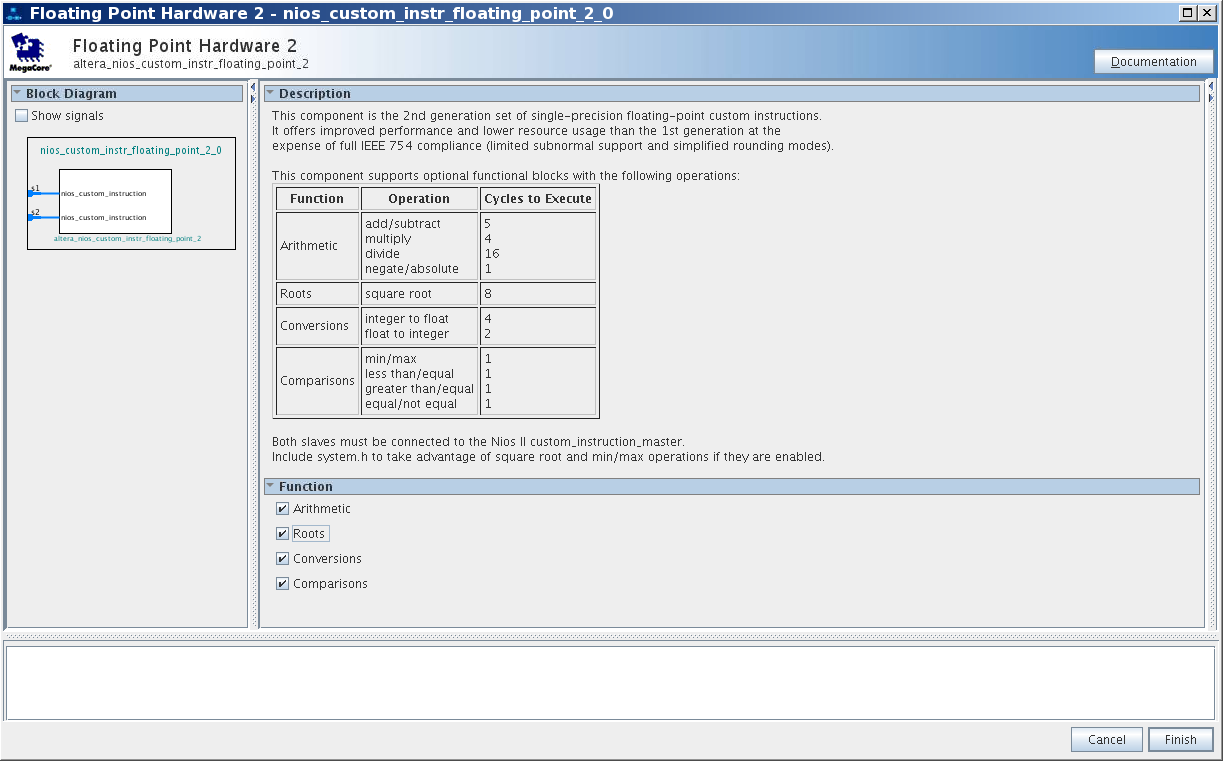

The FPH2 component editor, shown in the figure below, allows you to selectively enable any of several groups of floating point custom instructions. By default, all instructions are enabled.

In most cases, you should leave all floating point custom instructions enabled. However, for the MAX 10 device family in certain configurations, you might need to disable the Roots group.

MAX 10 devices cannot support the FPH2 square root instruction in the following configurations:

- Dual configuration mode

- Compressed configuration mode

- External RAM initialization disabled

The square root instruction uses a lookup table, requiring initialization that the MAX 10 cannot support in these configurations. Turn off the Roots option if you are targeting a MAX 10 device in one of these configurations.

When you disable one of the floating point instruction groups, software must implement the functions in that group (in this case, square root) if they are required. The BSP generator automatically creates this support. Refer to "Building the FPH2 Example Software" for details.

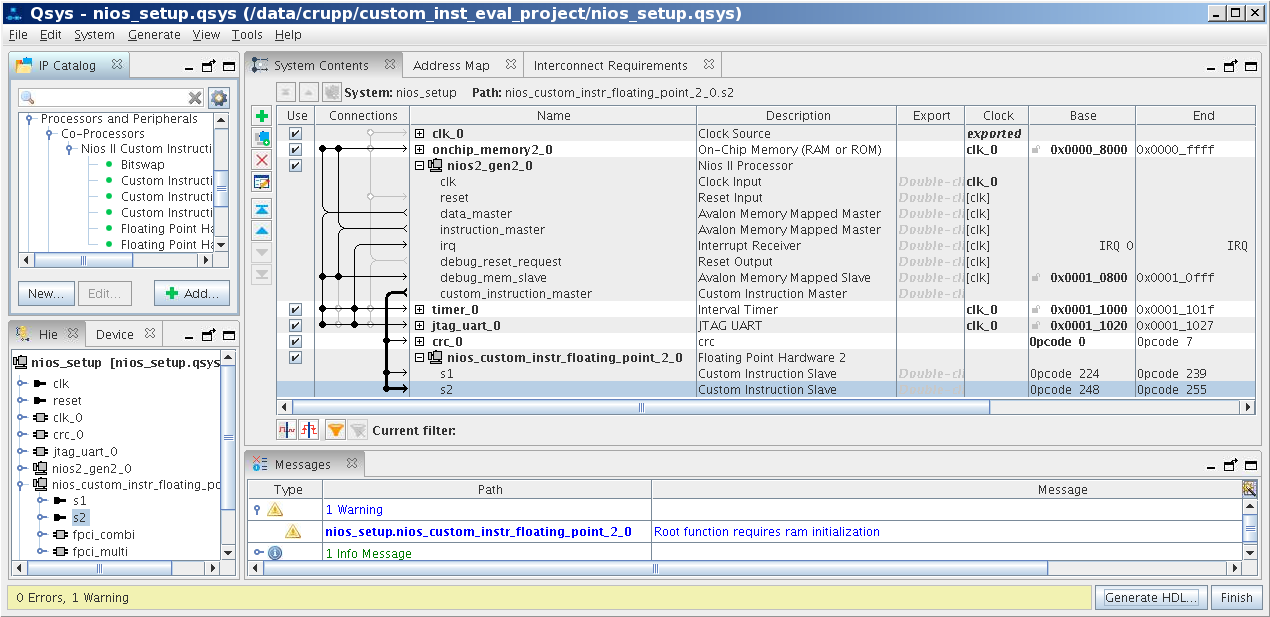

The example in the figure above targets a MAX 10 device. Note the warning message, reminding you that there could be an issue with RAM initialization for the square root function.

After connecting the FPH2 to the Nios II, generate your system in Platform Designer as you normally would. Then use the Quartus® Prime software to compile the generated RTL, or use an RTL simulator, like ModelSim* - Intel® FPGA Edition, to perform simulations.