Visible to Intel only — GUID: yga1656430039314

Ixiasoft

Visible to Intel only — GUID: yga1656430039314

Ixiasoft

2.3.2. Early Timing Analysis (Beta)

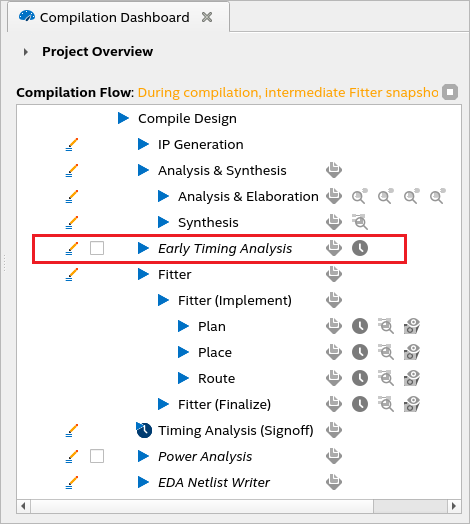

Once you enable the DNI flow, the compilation dashboard updates, and you can now access the Early Timing Analysis stage along with Analysis & Elaboration, as shown in the following image:

Early Timing Analysis flow is a combination of Synopsys* Design Constraint (SDC) on RTL and post-synthesis static timing analysis. However, you can run the flow even without RTL SDCs where you can view the post-synthesis timing netlist. For more information, refer to Synopsys* Design Constraint (SDC) on RTL and Post-Synthesis Static Timing Analysis (STA).

Early Timing Analysis flow involves running Analysis & Elaboration and Synthesis stages in conjunction with the Early Timing Analysis stage and iterating on your design's static timing analysis results early in the Intel® Quartus® Prime software compilation flow without running the Fitter. For additional information about each of the compilation stages listed in the Early Timing Analysis Flow, refer to the following topics: