Visible to Intel only — GUID: qdm1658977408130

Ixiasoft

2.1. Compilation Overview

2.2. Using the Compilation Dashboard

2.3. Design Netlist Infrastructure (Beta)

2.4. Design Synthesis

2.5. Design Place and Route

2.6. Incremental Optimization Flow

2.7. Fast Forward Compilation Flow

2.8. Full Compilation Flow

2.9. Exporting Compilation Results

2.10. Integrating Other EDA Tools

2.11. Synthesis Language Support

2.12. Compiler Optimization Techniques

2.13. Synthesis Settings Reference

2.14. Fitter Settings Reference

2.15. Design Compilation Revision History

2.9.1. Exporting a Version-Compatible Compilation Database

2.9.2. Importing a Version-Compatible Compilation Database

2.9.3. Creating a Design Partition

2.9.4. Exporting a Design Partition

2.9.5. Reusing a Design Partition

2.9.6. Viewing Quartus Database File Information

2.9.7. Clearing Compilation Results

3.1. Factors Affecting Compilation Results

3.2. Strategies to Reduce the Overall Compilation Time

3.3. Reducing Synthesis Time and Synthesis Netlist Optimization Time

3.4. Reducing Placement Time

3.5. Reducing Routing Time

3.6. Reducing Static Timing Analysis Time

3.7. Setting Process Priority

3.8. Reducing Compilation Time Revision History

Visible to Intel only — GUID: qdm1658977408130

Ixiasoft

2.3.1.6. Auto-hide Unconnected Pins

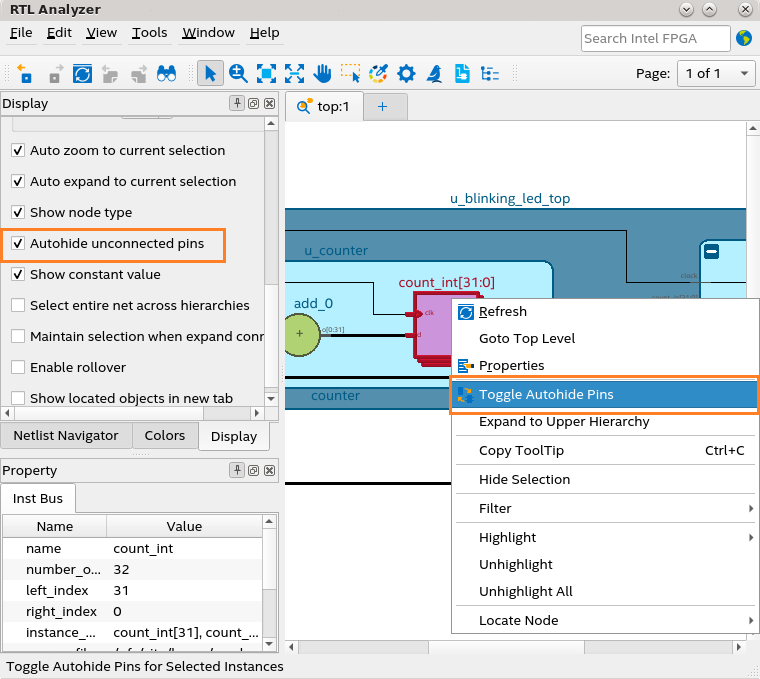

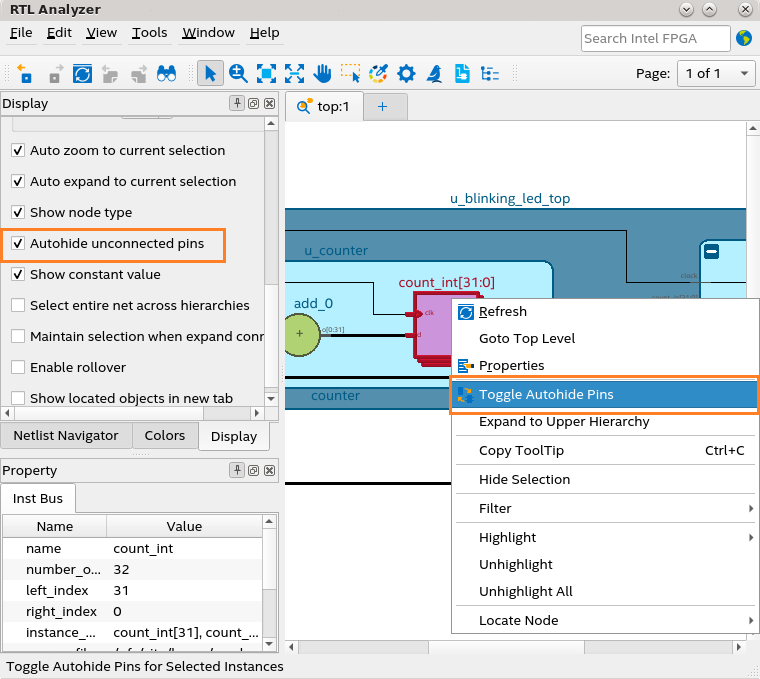

The Autohide unconnected pins option is enabled by default. Auto-hiding unconnected pins make the instance symbol less cluttered by hiding pins that are not connected to any net. You can disable this option when you want to view all pins or obtain properties of unconnected pins. You can either disable this mode for all instances in the Display setting or for a particular instance using the context-sensitive menu, as shown in the following image:

Figure 31. Auto-hiding Unconnected Pins