Intel® Quartus® Prime Pro Edition User Guide: Design Constraints

ID

683143

Date

9/26/2022

Public

A newer version of this document is available. Customers should click here to go to the newest version.

2.1.2.1. Specify Instance-Specific Constraints in Assignment Editor

2.1.2.2. Specifying Multi-Dimensional Bus Constraints

2.1.2.3. Specify I/O Constraints in Pin Planner

2.1.2.4. Plan Interface Constraints in Interface Planner and Tile Interface Planner

2.1.2.5. Adjust Constraints with the Chip Planner

2.1.2.6. Constraining Designs with the Design Partition Planner

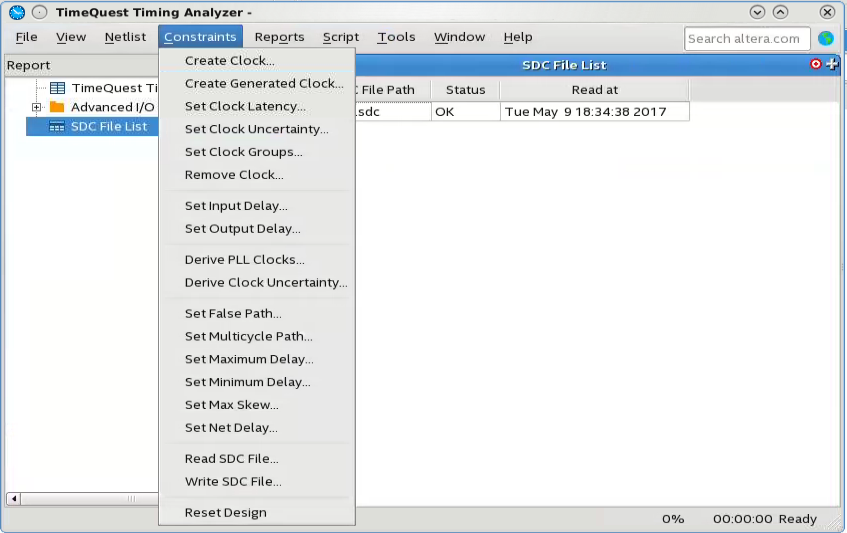

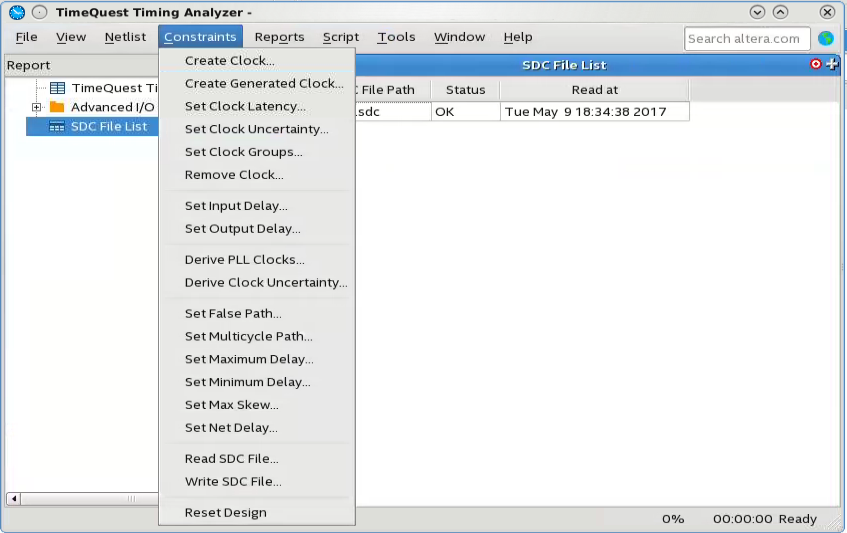

2.1.4. Specifying Timing Constraints in the GUI

You can specify timing constraints in the Timing Analyzer GUI. Click the Constraints menu in the Timing Analyzer to specify timing constraints that you can apply to your project.

Figure 5. Constraint menu in Timing Analyzer

When you specify a constraint in the GUI, the dialog box displays the equivalent SDC command syntax.

Create Clock Dialog Box

Individual timing assignments override project-wide requirements.

- To avoid reporting incorrect or irrelevant timing violations, you can assign timing exceptions to nodes and paths.

- The Timing Analyzer supports point-to-point timing constraints, wildcards to identify specific nodes when making constraints, and assignment groups to make individual constraints to groups of nodes.