Visible to Intel only — GUID: mwh1452708852228

Ixiasoft

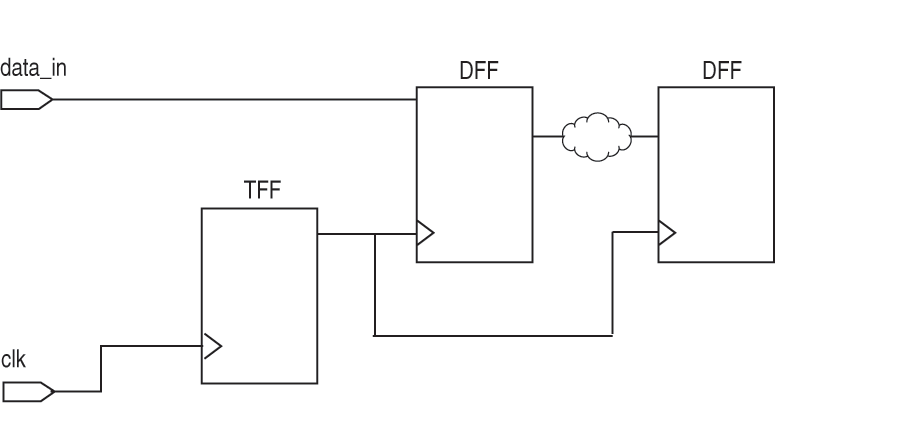

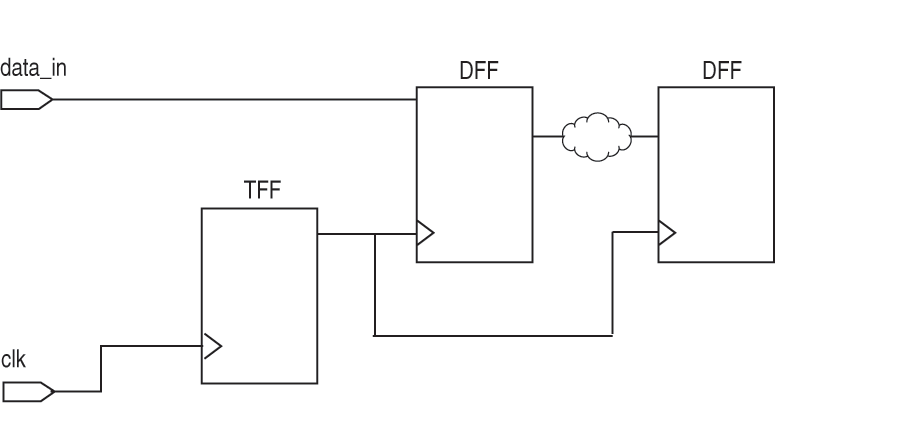

Toggle Register Generated Clock

Use a toggle register to create a divide-by-two clock. If the data feeding the toggle register is at a logical “1” value and fed by a 10 ns period clock, the output of the register is a clock with a period of 20 ns.

The constraints for the toggle register clock is very similar to the previous example.

Figure 5. Toggle Register Generating a Divide-by-Two Clock

Toggle Register Constraints

# Create a base clock

create_clock \

-period 10.000 \

-name clk \

[get_ports {clk}]

# Create the generated clock on the output

# of the toggle register.

create_generated_clock \

-name tff_clk \

-source [get_ports {clk}] \

-divide_by 2 \

[get_pins {tff|q}]