Visible to Intel only — GUID: isd1539121009101

Ixiasoft

Visible to Intel only — GUID: isd1539121009101

Ixiasoft

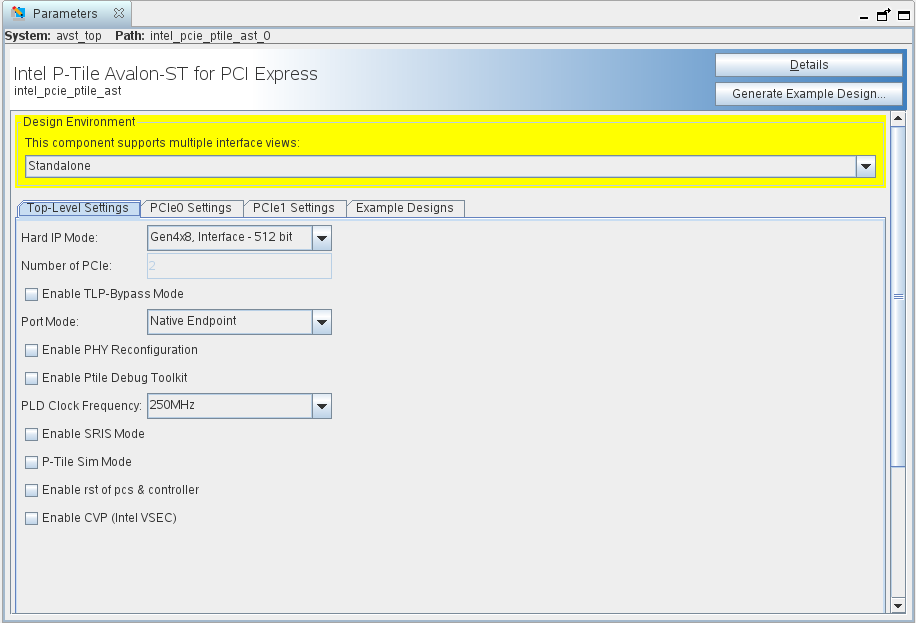

3.1. Top-Level Settings

| Parameter | Value | Default Value | Description |

|---|---|---|---|

| Hard IP Mode | Gen4x16, Interface - 512-bit Gen3x16, Interface - 512-bit Gen3x16, Interface - 256-bit Gen4x8, Interface - 512-bit Gen4x8, Interface - 256-bit Gen3x8, Interface - 256-bit Gen4x4, Interface - 128-bit Gen3x4, Interface - 128-bit |

Gen4x16, Interface - 512-bit |

Select the following elements:

Lane data rate:

Lane width:

|

| Number of PCIe | Total number of cores. This parameter is set by the choice made for Hard IP Mode. | ||

| Port Mode | Root Port Native Endpoint

Note: These are the available options when Enable TLP Bypass is set to False. If TLP Bypass mode is enabled, refer to the table Port Mode Options in TLP Bypass below for available port mode options.

|

Native Endpoint |

Specifies the port type. |

| Enable PHY Reconfiguration | True/False | False | Enable the PHY Reconfiguration Interface. |

| Enable Ptile Debug Toolkit | True/False | False | Enable the P-Tile Debug Toolkit for JTAG-based System Console debug access. |

| PLD Clock Frequency | 500 MHz 450 MHz 400 MHz 350 MHz 250 MHz 225 MHz 200 MHz 175 MHz |

400 MHz (for Gen4 modes) 250 MHz (for Gen3 modes) |

Select the frequency of the Application clock. The options available vary depending on the setting of the Hard IP Mode parameter. For Gen4 modes, the available clock frequencies are 500MHz/450MHz/400MHz/350MHz/250MHz/225MHz/200MHz/175MHz (for Intel® Agilex™ ) and 450MHz/400MHz/350MHz/225MHz/200MHz/175MHz (for Intel® Stratix® 10 DX). For Gen3 modes, the available clock frequency is 250 MHz (for Intel® Agilex™ and Intel® Stratix® 10 DX). |

| Enable TLP Bypass | True/False | False |

Enable the TLP Bypass feature.

Note:

For configurations where multiple ports are available, it is possible to enable TLP Bypass on a per-port basis. Refer to Table 12 for the available port modes and configurations.

|

| Enable SRIS Mode | True/False | False | Enable the Separate Reference Clock with Independent Spread Spectrum Clocking (SRIS) feature. When you enable this option, the Slot clock configuration option under the PCIeN Settings → PCIeN PCI Express/PCI Capabilities → PCIeN Link tab will be automatically disabled. |

| P-Tile Sim Mode | True/False | False | Enabling this parameter reduces the simulation time of Hot Reset tests by 5 ms.

Note: Do not enable this option if you need to run synthesis.

|

| Enable RST of PCS & Controller | True/False | False | Enable the reset of PCS and Controller in User Mode for Endpoint and Bypass Upstream modes. When this parameter is True, depending on the topology, new signals (p<n>_pld_clrpcs_n) are exported to the Avalon® Streaming interface. When this parameter is False (default), the IP internally ties off these signals instead of exporting them.

Note: This parameter is required for the independent reset feature, which is only supported in the x8x8 Endpoint/Endpoint mode.

Note: Refer to Appendix E for more details regarding the independent resets feature and its usage.

|

| Enable CVP (Intel VSEC) | True/False | False | Enablement of CVP for a single tile only. Refer to https://www.intel.com/content/www/us/en/programmable/documentation/yiz1574399366423.html for more details on CVP. |

| Configuration | Available Port Modes | |||

|---|---|---|---|---|

| Port 0 | Port 1 | Port 2 | Port 3 | |

| 1x16 (Gen4x16 or Gen3x16) | TLP Bypass On : Downstream (Default) |

N/A |

N/A |

N/A |

| TLP Bypass On : Upstream |

||||

| 2x8 (Gen4x8/Gen4x8 or Gen3x8/Gen3x8) | TLP Bypass On : Downstream (Default) |

TLP Bypass On : Downstream (Default) | N/A |

N/A |

| TLP Bypass On : Upstream |

TLP Bypass On : Upstream |

|||

| TLP Bypass Off : Endpoint |

TLP Bypass On : Upstream |

|||

| TLP Bypass On : Upstream |

TLP Bypass On : Downstream |

|||

| TLP Bypass On : Upstream |

TLP Bypass Off : Endpoint |

|||

| 4x4 (Gen4x4/Gen4x4 / Gen4x4/Gen4x4 or Gen3x4/Gen3x4 / Gen3x4/Gen3x4) | TLP Bypass On : Downstream (Default) |

TLP Bypass On : Downstream (Default) |

TLP Bypass On : Downstream (Default) |

TLP Bypass On : Downstream (Default) |

| TLP Bypass On : Upstream |

TLP Bypass On : Upstream |

TLP Bypass On : Upstream |

TLP Bypass On : Upstream |

|