Visible to Intel only — GUID: uim1710446693130

Ixiasoft

2.4. Compiling and Simulating the Design

The design example testbench simulates your generated design.

- Change the working directory to <example_design_directory>/ed_sim.

- Run the simulation script for the simulator of your choice.

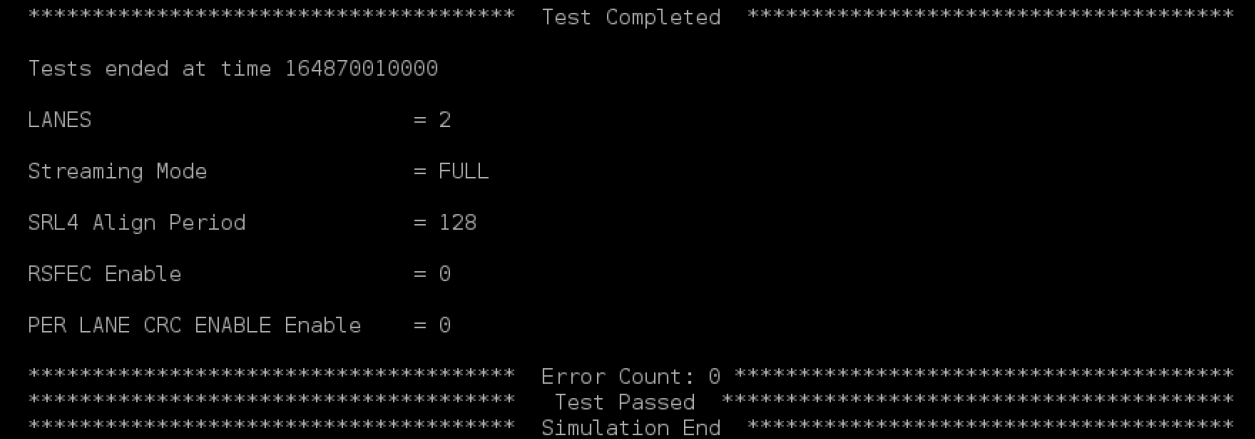

Table 5. Testbench Simulation Scripts Simulator File Directory Command Questa* Intel® FPGA Edition <variation name>intel_sl4_gts_0_example_design/ed_sim source run_mentor.tcl Note: source evaluates a file or resource as a Tcl script (Tools - Tcl - Execute - Macro).QuestaSim* VCS* <variation name>intel_sl4_gts_0_example_design/ed_sim sh run_vcs.sh VCS* MX <variation name>intel_sl4_gts_0_example_design/ed_sim sh run_vcsmx.sh Xcelium* <variation name>intel_sl4_gts_0_example_design/ed_sim sh run_xcelium.sh Riviera-PRO* <variation name>intel_sl4_gts_0_example_design/ed_sim riviera -do run_riviera.do - When the simulation is complete, you can now analyze the results and verify the design. A successful simulation ends with the following message, "Test Passed."

Note: LANES, Streaming Mode, and RSFEC Enable may vary according to their parameters.