Visible to Intel only — GUID: ogy1699987935137

Ixiasoft

1. About the GTS JESD204C Intel® FPGA IP User Guide

2. Overview of the GTS JESD204C Intel® FPGA IP

3. Functional Description

4. Getting Started

5. Designing with the GTS JESD204C Intel® FPGA IP

6. GTS JESD204C Intel® FPGA IP Parameters

7. Interface Signals

8. Document Revision History for the GTS JESD204C Intel® FPGA IP User Guide

4.1. Installing and Licensing Intel® FPGA IP Cores

4.2. Intel® FPGA IP Evaluation Mode

4.3. IP Catalog and Parameter Editor

4.4. GTS JESD204C IP Component Files

4.5. Creating a New Quartus® Prime Project

4.6. Parameterizing and Generating the IP

4.7. Compiling the GTS JESD204C IP Design

4.8. Programming an FPGA Device

5.1. Configuring the GTS Reset Sequencer Intel® FPGA IP

5.2. Reset Initialization

5.3. Configuration Phase

5.4. Link Reinitialization

5.5. SYSREF Sampling

5.6. Interrupt and Error Handling

5.7. Multi-Device Synchronization

5.8. Deterministic Latency

5.9. Dual Simplex Support

5.10. Analog Parameter Settings

5.11. Transceiver Toolkit

Visible to Intel only — GUID: ogy1699987935137

Ixiasoft

3.1.3. GTS Reset Sequencer Intel® FPGA IP Clock

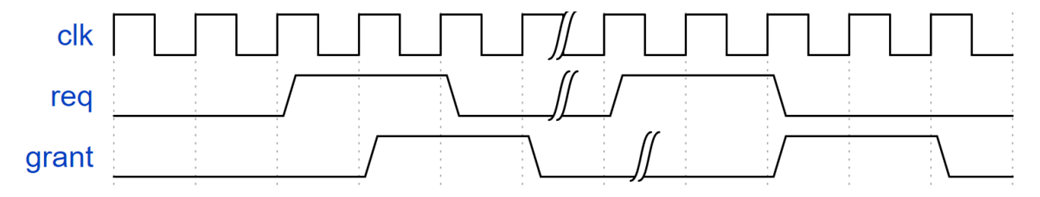

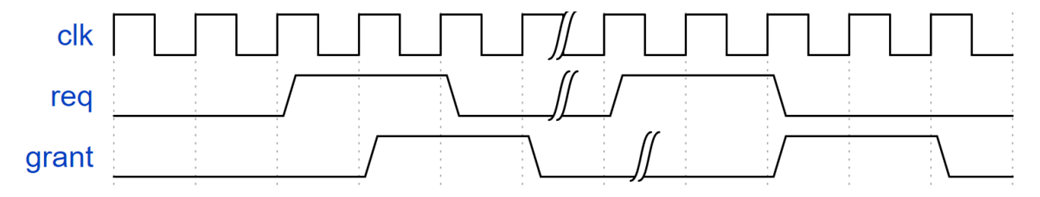

Figure 5. GTS Reset Sequencer Intel® FPGA IP Interface Timing Diagram

req refers to request signal from the SRC to the GTS Reset Sequencer Intel® FPGA IP for reset operation. It asserts when there is a request to toggle reset.

The grant signal is from the GTS Reset Sequencer Intel® FPGA IP to the SRC. It asserts when the reset request is granted by the Reset Sequencer.

This signal handshake between req and grant is an internal process that operates without user intervention.

Related Information