Visible to Intel only — GUID: cqf1660068224928

Ixiasoft

1. About the External Memory Interfaces Intel Agilex® 7 M-Series FPGA IP

2. Design Example Quick Start Guide for External Memory Interfaces Intel Agilex® 7 M-Series FPGA IP

3. Design Example Description for External Memory Interfaces Intel Agilex® 7 M-Series FPGA IP

4. Document Revision History for External Memory Interfaces Intel Agilex® 7 M-Series FPGA IP Design Example User Guide

2.1. Creating an EMIF Project

2.2. Generating and Configuring the EMIF IP

2.3. Configuring DQ Pin Swizzling

2.4. Generating the Synthesizable EMIF Design Example

2.5. Generating the EMIF Design Example for Simulation

2.6. Pin Placement for Intel Agilex® 7 M-Series EMIF IP

2.7. Compiling the Intel Agilex® 7 M-Series EMIF Design Example

2.8. Generating the EMIF Design Example with the Performance Monitor

2.1.1.3.1. Generating a Custom Memory Preset File for DDR4

2.1.1.3.2. Guidelines for Selecting the DDR4 DRAM Component Package Type

2.1.1.3.3. Generating a Custom Memory Preset File for DDR5

2.1.1.3.4. Guidelines for Selecting the DDR5 DRAM Component Package Type

2.1.1.3.5. Generating a Custom Memory Preset File for LPDDR5

2.3.1. Example: DQ Pin Swizzling Within DQS group for x32 DDR4 interface

2.3.2. Example: Byte Swizzling for a x32 DDR4 interface, using a memory device of x8 width

2.3.3. Combining Pin and Byte Swizzling

2.3.4. Example: Swizzling for a x32 + ECC interface

2.3.5. Example: Byte Swizzling for Lockstep Configuration

Visible to Intel only — GUID: cqf1660068224928

Ixiasoft

2.5. Generating the EMIF Design Example for Simulation

For the Intel Agilex® 7 M-Series development kit, it is sufficient to leave most of the Intel Agilex® 7 M-Series EMIF IP settings at their default values. To generate the design example for simulation, follow these steps:

- On the Example Designs tab, ensure that the Simulation box is set as True. Also choose the required Simulation HDL format, either Verilog or VHDL.

- Configure the EMIF IP and click File > Save to save the current setting into the user IP variation file (<user instance name>.ip).

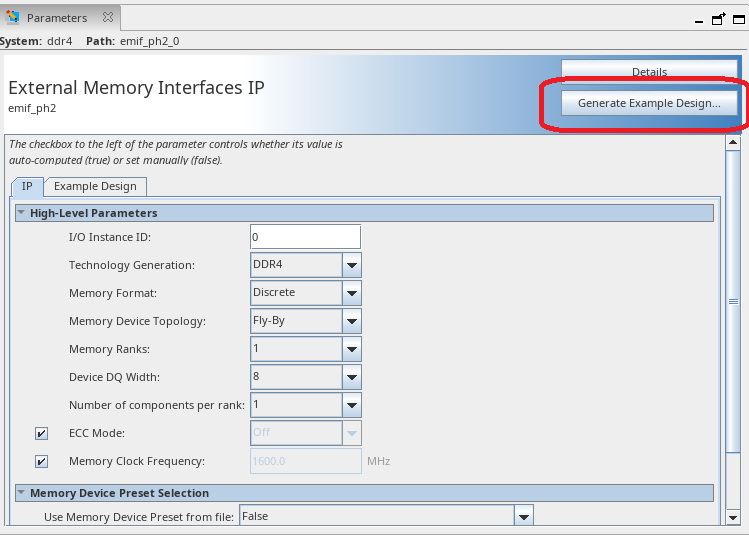

- Click Generate Example Design in the upper-right corner of the window.

Figure 34. Generate Example Design

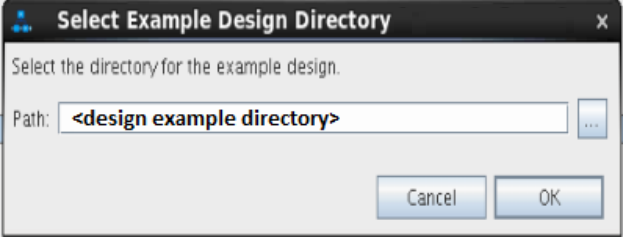

- Specify a directory for the EMIF design example and click OK. Successful generation of the EMIF design example creates multiple file sets for various supported simulators, under a sim/ed_sim directory.

Figure 35. Specifying a Directory

- Click File > Exit to exit the IP Parameter Editor Pro window. The system prompts, Recent changes have not been generated. Generate now? Click No to continue with the next flow.

Figure 36. Generated Simulation Design Example File Structure

Note: The External Memory Interfaces Intel Agilex® 7 M-Series FPGA IP currently supports only the VCS, ModelSim/QuestaSim, and Xcelium simulators.

Note: The External Memory Interfaces Intel Agilex® 7 M-Series FPGA IP currently supports only the VCS, ModelSim/QuestaSim, and Xcelium simulators.

Note:

If you don't select the Simulation or Synthesis checkbox, the destination directory contains only Platform Designer design files, which the Intel® Quartus® Prime software cannot compile directly, but which you can view or edit in the Platform Designer. In this situation you can run the following commands to generate synthesis and simulation file sets:

- To create an Intel® Quartus® Prime software-compilable project, run the

quartus_sh -t make_qii_design.tcl

script in the destination directory. - To create a simulation project, run the

quartus_sh -t make_sim_design.tcl

script in the destination directory.

Note: If you have generated a design example and then make changes to it in the parameter editor, you must regenerate the design example to see your changes implemented. The newly generated design example does not overwrite the existing design example files.

Note: For information on simulating the external memory interface IP, refer to Running Simulation .