Visible to Intel only — GUID: mmk1660068173304

Ixiasoft

1. About the External Memory Interfaces Intel Agilex® 7 M-Series FPGA IP

2. Design Example Quick Start Guide for External Memory Interfaces Intel Agilex® 7 M-Series FPGA IP

3. Design Example Description for External Memory Interfaces Intel Agilex® 7 M-Series FPGA IP

4. Document Revision History for External Memory Interfaces Intel Agilex® 7 M-Series FPGA IP Design Example User Guide

2.1. Creating an EMIF Project

2.2. Generating and Configuring the EMIF IP

2.3. Configuring DQ Pin Swizzling

2.4. Generating the Synthesizable EMIF Design Example

2.5. Generating the EMIF Design Example for Simulation

2.6. Pin Placement for Intel Agilex® 7 M-Series EMIF IP

2.7. Compiling the Intel Agilex® 7 M-Series EMIF Design Example

2.1.1.3.12.1.1.3.32.1.1.3.5. Generating a Custom Memory Preset File for DDR42.1.1.3.12.1.1.3.32.1.1.3.5. Generating a Custom Memory Preset File for DDR42.1.1.3.12.1.1.3.32.1.1.3.5. Generating a Custom Memory Preset File for DDR4

2.1.1.3.2. Guidelines for Selecting the DDR4 DRAM Component Package Type

2.1.1.3.12.1.1.3.32.1.1.3.5. Generating a Custom Memory Preset File for DDR42.1.1.3.12.1.1.3.32.1.1.3.5. Generating a Custom Memory Preset File for DDR42.1.1.3.12.1.1.3.32.1.1.3.5. Generating a Custom Memory Preset File for DDR4

2.1.1.3.4. Guidelines for Selecting the DDR5 DRAM Component Package Type

2.1.1.3.12.1.1.3.32.1.1.3.5. Generating a Custom Memory Preset File for DDR42.1.1.3.12.1.1.3.32.1.1.3.5. Generating a Custom Memory Preset File for DDR42.1.1.3.12.1.1.3.32.1.1.3.5. Generating a Custom Memory Preset File for DDR4

2.3.1. Example: DQ Pin Swizzling Within DQS group for x32 DDR4 interface

2.3.2. Example: Byte Swizzling for a x32 DDR4 interface, using a memory device of x8 width

2.3.3. Combining Pin and Byte Swizzling

2.3.4. Example: Swizzling for a x32 + ECC interface

2.3.5. Example: Byte Swizzling for Lockstep Configuration

Visible to Intel only — GUID: mmk1660068173304

Ixiasoft

2.2. Generating and Configuring the EMIF IP

The following steps illustrate how to generate and configure the EMIF IP. This walkthrough creates a DDR5 interface, but the steps are similar for other protocols. (These steps follow the IP Catalog (standalone) flow; if you choose to use the Platform Designer (system) flow instead, the steps are similar.)

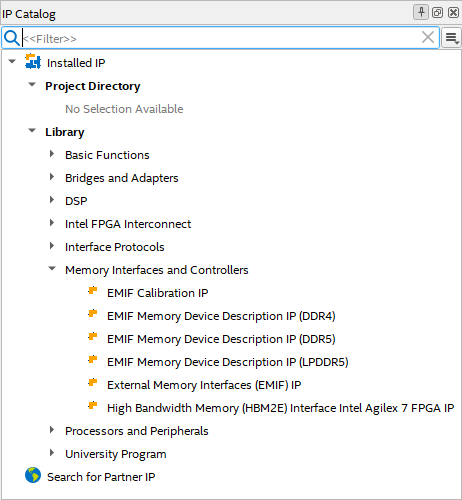

- In the IP Catalog window, select External Memory Interfaces IP. (If the IP Catalog window is not visible, select View > IP Catalog.)

Figure 17. IP Catalog

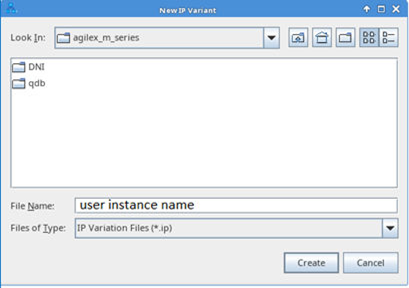

- In the IP Parameter Editor, provide an entity name for the EMIF IP (the name that you provide here becomes the file name for the IP) and specify a directory. Click Create.

Figure 18. Specifying a File name

- The parameter editor has multiple tabs where you must configure parameters to reflect your EMIF implementation.