2.3. Configuring DQ Pin Swizzling

Do not change the location for the EMIF pin using a .qsf assignment or the pin planner if you need to swap the DQ pins within a DQS group or the DQS group to simplify board design. For example, if you implement a x32 DDR4 interface, the EMIF pin location must adhere to the x32 column in the DDR4 Pin Placement table in the Product Architecture chapter of the External Memory Interfaces Intel Agilex® 7 M-Series FPGA IP User Guide. There is no flexibility to swap the address command pin location.

Example: DQ Pin Swizzling Within DQS group for x32 DDR4 interface

This example uses the lane placement of the following table, with a x8 DQ width.

| Lane Number | BL7 | BL6 | BL5 | BL4 | BL3 | BL2 | BL1 | BL0 |

|---|---|---|---|---|---|---|---|---|

| Default placement | GPIO | DQS[3] | DQS[2] | DQS[1] | AC[2] | AC[1] | AC[0] | DQS[0] |

| Lane | Pin Index | DDR4 x32 (Default Placement) | After Swizzling / Swapping |

|---|---|---|---|

| BL0 | 11 | MEM_DQ[7] | MEM_DQ[6] |

| 10 | MEM_DQ[6] | MEM_DQ[5] | |

| 9 | MEM_DQ[5] | MEM_DQ[7] | |

| 8 | MEM_DQ[4] | MEM_DQ[4] | |

| 7 | |||

| 6 | MEM_DM_N[0] | MEM_DM_N[0] | |

| 5 | MEM_DQS_C[0] | MEM_DQS_C[0] | |

| 4 | MEM_DQS_T[0] | MEM_DQS_T[0] | |

| 3 | MEM_DQ[3] | MEM_DQ[0] | |

| 2 | MEM_DQ[2] | MEM_DQ[2] | |

| 1 | MEM_DQ[1] | MEM_DQ[1] | |

| 0 | MEM_DQ[0] | MEM_DQ[3] |

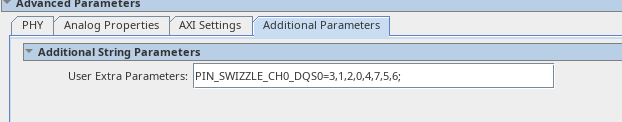

To achieve this swizzling in DQS group 0, you must enter PIN_SWIZZLE_CH0_DQS0=3,1,2,0,4,7,5,6; in the User Extra Parameters field of the Additional Parameters tab in the Advanced Parameters section of the General IP Parameters tab in the External Memory Interfaces IP parameter editor.

| Lane | Pin Index | DDR4 x32 (from table) | After Swizzling / Swapping |

|---|---|---|---|

| BL5 | 71 | MEM_DQ[23] | MEM_DQ[17] |

| 70 | MEM_DQ[22] | MEM_DQ[22] | |

| 69 | MEM_DQ[21] | MEM_DQ[21] | |

| 68 | MEM_DQ[20] | MEM_DQ[20] | |

| 67 | |||

| 66 | MEM_DM_N[2] | MEM_DM_N[2] | |

| 65 | MEM_DQS_C[2] | MEM_DQS_C[2] | |

| 64 | MEM_DQS_T[2] | MEM_DQS_T[2] | |

| 63 | MEM_DQ[19] | MEM_DQ[19] | |

| 62 | MEM_DQ[18] | MEM_DQ[18] | |

| 61 | MEM_DQ[17] | MEM_DQ[23] | |

| 60 | MEM_DQ[16] | MEM_DQ[16] |

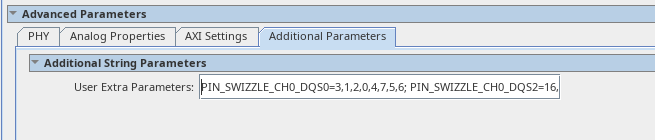

To achieve this swizzling in DQS Group 2, you must enter PIN_SWIZZLE_CH0_DQS2=16,23,18,19,20,21,22,17; in the User Extra Parameters field of the Additional Parameters tab in the Advanced Parameters section of the General IP Parameters tab in the External Memory Interfaces IP parameter editor.

You can enter multiple specifications in the User Extra Parameters field, each separated by a comma.

Example: Byte Swizzling for a x32 DDR4 interface, implemented with x8 DQS group

| Lane Number | BL0 | BL1 | BL2 | BL3 | BL4 | BL5 | BL6 | BL7 |

|---|---|---|---|---|---|---|---|---|

| Default Placement | DQ[0] | AC[0] | AC[1] | AC[2] | DQ[1] | DQ[2] | DQ[3] | GPIO |

| After Byte Swizzling | DQ[2] | AC[0] | AC[1] | AC[2] | DQ[1] | DQ[0] | DQ[3] | GPIO |

| BYTE SWIZZLE | 2 | X | X | X | 1 | 0 | 3 | X |

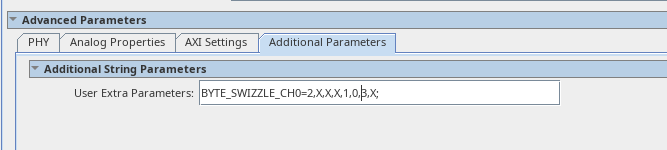

This example illustrates swizzling DQS group 0 with DQS group 2. The BYTE_SWIZZLE denotes the DQS group implemented in the lane after the swizzling. X indicates that the lane is not used as a data lane (meaning that it serves as an address/command lane or is not used by the EMIF interface).

To achieve this swizzling, you must enter BYTE_SWIZZLE_CH0=2,X,X,X,1,0,3,X”; in the User Extra Parameters field of the Additional Parameters tab in the Advanced Parameters section of the General IP Parameters tab in the External Memory Interfaces IP parameter editor.

Example : Combining Pin and Byte Swizzling

This example combines the two previous examples, entering the following swizzle parameters:

- PIN_SWIZZLE_CH0_DQS0=3,1,2,0,4,7,5,6;

- PIN_SWIZZLE_CH0_DQS2=16,23,18,19,20,21,22,17;

- BYTE_SWIZZLE_CH0=2,X,X,X,1,0,3,X;

The following table shows the resulting pin placement after DQ pin and byte swizzling.

| Lane | Pin Index | Default | Effective Pinout |

|---|---|---|---|

| BL5 | 71 | MEM_DQ[23] | MEM_DQ[6] |

| 70 | MEM_DQ[22] | MEM_DQ[5] | |

| 69 | MEM_DQ[21] | MEM_DQ[7] | |

| 68 | MEM_DQ[20] | MEM_DQ[4] | |

| 67 | |||

| 66 | MEM_DM_N[2] | MEM_DM_N[0] | |

| 65 | MEM_DQS_C[2] | MEM_DQS_C[0] | |

| 64 | MEM_DQS_T[2] | MEM_DQS_T[0] | |

| 63 | MEM_DQ[19] | MEM_DQ[0] | |

| 62 | MEM_DQ[18] | MEM_DQ[2] | |

| 61 | MEM_DQ[17] | MEM_DQ[1] | |

| 60 | MEM_DQ[16] | MEM_DQ[3] | |

| BL0 | 11 | MEM_DQ[7] | MEM_DQ[17] |

| 10 | MEM_DQ[6] | MEM_DQ[22] | |

| 9 | MEM_DQ[5] | MEM_DQ[21] | |

| 8 | MEM_DQ[4] | MEM_DQ[20] | |

| 7 | |||

| 6 | MEM_DM_N[0] | MEM_DM_N[2] | |

| 5 | MEM_DQS_C[0] | MEM_DQS_C[2] | |

| 4 | MEM_DQS_T[0] | MEM_DQS_T[2] | |

| 3 | MEM_DQ[3] | MEM_DQ[19] | |

| 2 | MEM_DQ[2] | MEM_DQ[18] | |

| 1 | MEM_DQ[1] | MEM_DQ[23] | |

| 0 | MEM_DQ[0] | MEM_DQ[16] |

When using the EMIF IP with 2 channels , the syntax for CH0 and CH1 must be the following:

- PIN_SWIZZLE_CH0_DQS0/ PIN_SWIZZLE_CH1_DQS0

- PIN_SWIZZLE_CH0_DQS2/ PIN_SWIZZLE_CH1_DQS2

- BYTE_SWIZZLE_CH0/ BYTE_SWIZZLE_CH1