Visible to Intel only — GUID: pgx1654092442863

Ixiasoft

1. About the F-Tile Dynamic Reconfiguration Suite Core

2. Interface Overview

3. Parameters

4. Designing with the IP Core

5. Block Description

6. Configuration Registers

7. F-Tile Dynamic Reconfiguration Suite Intel® FPGA IP User Guide Archives

8. Document Revision History for the F-Tile Dynamic Reconfiguration Suite User Guide

4.1. Generating Dynamic Reconfiguration Design and Configuration Profiles

4.2. Dynamic Reconfiguration QSF Settings

4.3. Dynamic Reconfiguration Using QSF-driven Flow

4.4. Dynamic Reconfiguration Rules

4.5. Hardware States and Configuration Profiles

4.6. Nios® -Based Dynamic Reconfiguration Flow

4.7. Using the Tile Assignment Editor

4.8. Visualizing Dynamic Reconfiguration Group Placement

4.9. Assigning IP_COLOCATE Hierarchy

4.10. Example: Dynamic Reconfiguration with Multirate IP Flow

4.11. Example: Dynamic Reconfiguration Programming Sequence

4.12. Dynamic Reconfiguration Error Recovery Handling

4.13. Determining Profile Numbers

4.14. Master Clock Channel

4.15. Using the IP_RECONFIG_GROUP_PARENT QSF Assignment

4.16. Simulating the IP Core

6.1. Dynamic Reconfiguration New Trigger

6.2. Dynamic Reconfiguration Next Profile 0

6.3. Dynamic Reconfiguration Next Profile 1

6.4. Dynamic Reconfiguration Next Profile 2

6.5. Dynamic Reconfiguration Next Profile 3

6.6. Dynamic Reconfiguration Next Profile 4

6.7. Dynamic Reconfiguration Next Profile 5

6.8. Dynamic Reconfiguration Next Profile 6

6.9. Dynamic Reconfiguration Next Profile 7

6.10. Dynamic Reconfiguration Next Profile 8

6.11. Dynamic Reconfiguration Next Profile 9

6.12. Dynamic Reconfiguration Next Profile 10

6.13. Dynamic Reconfiguration Next Profile 11

6.14. Dynamic Reconfiguration Next Profile 12

6.15. Dynamic Reconfiguration Next Profile 13

6.16. Dynamic Reconfiguration Next Profile 14

6.17. Dynamic Reconfiguration Next Profile 15

6.18. Dynamic Reconfiguration Next Profile 16

6.19. Dynamic Reconfiguration Next Profile 17

6.20. Dynamic Reconfiguration Next Profile 18

6.21. Dynamic Reconfiguration Next Profile 19

6.22. Dynamic Reconfiguration Avalon MM Timeout

6.23. Dynamic Reconfiguration TX Channel Reconfiguration

6.24. Dynamic Reconfiguration RX Channel Reconfiguration

6.25. Dynamic Reconfiguration TX Channel in Reset Acknowledgment

6.26. Dynamic Reconfiguration TX Channel out of Reset

6.27. Dynamic Reconfiguration TX Channel Reset Control Init Status

6.28. Dynamic Reconfiguration TX Channel Source Alarm

6.29. Dynamic Reconfiguration RX Channel in Reset Acknowledgment

6.30. Dynamic Reconfiguration RX Channel out of Reset

6.31. Dynamic Reconfiguration RX Channel Reset Control Init Status

6.32. Dynamic Reconfiguration RX Channel Source Alarm

6.33. Dynamic Reconfiguration Local Error Status

Visible to Intel only — GUID: pgx1654092442863

Ixiasoft

4.7. Using the Tile Assignment Editor

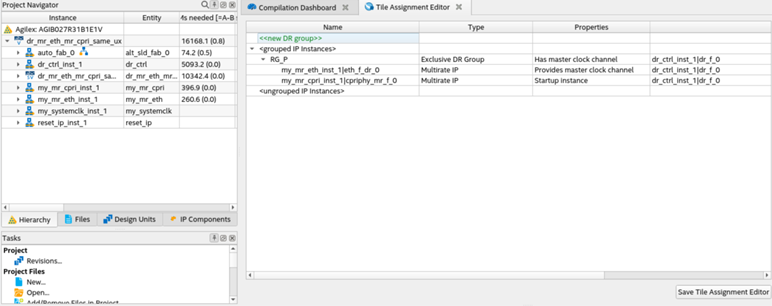

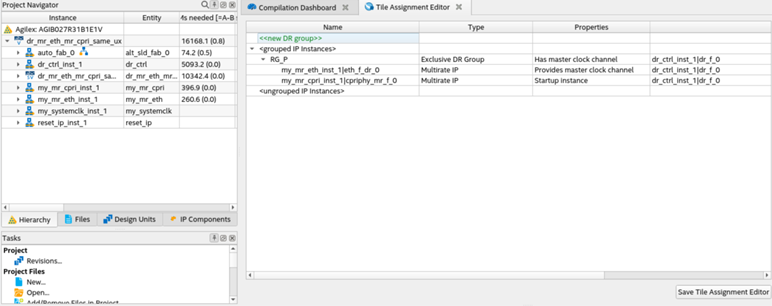

To create qsf assignments consisting of discreet IPs, you can use the Tile Assignment Editor. To open the Tile Assignment Editor: click Quartus® Prime Menu > Assignments > Tile Assignment Editor.

Figure 5. Tile Assignment Editor

The Tile Assignment Editor consists of the following three sections:

- New DR Group

To create new Dynamic Reconfiguration group and it’s associated attributes. The associated attributes are:

- Group Name: Each reconfiguration group must have a unique, user-selected name.

- Group Type: Exclusive means that the group can only be active by itself. Inclusive means that the group can be active with other Dynamic Reconfiguration groups.

- Reconfiguration Controller: Provides the hierarchical path to the Reconfiguration Controller IP.

- Has Master Clock Channel: Select if you want to specify the Master Clock Channel for the Dynamic Reconfiguration group. If you do not specify the Master Clock Channel, the Quartus Support Logic Generation makes a default selection.

- Building block instance name: Provides the name of the building block associated with the master clock channel.

- Clock port: Provides the name of the clock port on the BB instance which is the master clock channel.

- Grouped IP Instances

Shows current list of IPs which have been assigned to Dynamic Reconfiguration groups and their associated attributes. The IPs are listed in hierarchical order. You can select the following associated attribute for each IP:

- Is startup instance: Allows you to determine which IP within the Dynamic Reconfiguration group is active at startup for either hardware or simulation.

- Ungrouped IP Instances

Shows current list of IPs for which you can define a Dynamic Reconfiguration group. When these IPs are added to a Dynamic Reconfiguration group, they disappear from this list.