Visible to Intel only — GUID: ydr1654092549357

Ixiasoft

1. About the F-Tile Dynamic Reconfiguration Suite Core

2. Interface Overview

3. Parameters

4. Designing with the IP Core

5. Block Description

6. Configuration Registers

7. F-Tile Dynamic Reconfiguration Suite Intel® FPGA IP User Guide Archives

8. Document Revision History for the F-Tile Dynamic Reconfiguration Suite User Guide

4.1. Generating Dynamic Reconfiguration Design and Configuration Profiles

4.2. Dynamic Reconfiguration QSF Settings

4.3. Dynamic Reconfiguration Using QSF-driven Flow

4.4. Dynamic Reconfiguration Rules

4.5. Hardware States and Configuration Profiles

4.6. Nios® -Based Dynamic Reconfiguration Flow

4.7. Using the Tile Assignment Editor

4.8. Visualizing Dynamic Reconfiguration Group Placement

4.9. Assigning IP_COLOCATE Hierarchy

4.10. Example: Dynamic Reconfiguration with Multirate IP Flow

4.11. Example: Dynamic Reconfiguration Programming Sequence

4.12. Dynamic Reconfiguration Error Recovery Handling

4.13. Determining Profile Numbers

4.14. Master Clock Channel

4.15. Using the IP_RECONFIG_GROUP_PARENT QSF Assignment

4.16. Simulating the IP Core

6.1. Dynamic Reconfiguration New Trigger

6.2. Dynamic Reconfiguration Next Profile 0

6.3. Dynamic Reconfiguration Next Profile 1

6.4. Dynamic Reconfiguration Next Profile 2

6.5. Dynamic Reconfiguration Next Profile 3

6.6. Dynamic Reconfiguration Next Profile 4

6.7. Dynamic Reconfiguration Next Profile 5

6.8. Dynamic Reconfiguration Next Profile 6

6.9. Dynamic Reconfiguration Next Profile 7

6.10. Dynamic Reconfiguration Next Profile 8

6.11. Dynamic Reconfiguration Next Profile 9

6.12. Dynamic Reconfiguration Next Profile 10

6.13. Dynamic Reconfiguration Next Profile 11

6.14. Dynamic Reconfiguration Next Profile 12

6.15. Dynamic Reconfiguration Next Profile 13

6.16. Dynamic Reconfiguration Next Profile 14

6.17. Dynamic Reconfiguration Next Profile 15

6.18. Dynamic Reconfiguration Next Profile 16

6.19. Dynamic Reconfiguration Next Profile 17

6.20. Dynamic Reconfiguration Next Profile 18

6.21. Dynamic Reconfiguration Next Profile 19

6.22. Dynamic Reconfiguration Avalon MM Timeout

6.23. Dynamic Reconfiguration TX Channel Reconfiguration

6.24. Dynamic Reconfiguration RX Channel Reconfiguration

6.25. Dynamic Reconfiguration TX Channel in Reset Acknowledgment

6.26. Dynamic Reconfiguration TX Channel out of Reset

6.27. Dynamic Reconfiguration TX Channel Reset Control Init Status

6.28. Dynamic Reconfiguration TX Channel Source Alarm

6.29. Dynamic Reconfiguration RX Channel in Reset Acknowledgment

6.30. Dynamic Reconfiguration RX Channel out of Reset

6.31. Dynamic Reconfiguration RX Channel Reset Control Init Status

6.32. Dynamic Reconfiguration RX Channel Source Alarm

6.33. Dynamic Reconfiguration Local Error Status

Visible to Intel only — GUID: ydr1654092549357

Ixiasoft

4.13. Determining Profile Numbers

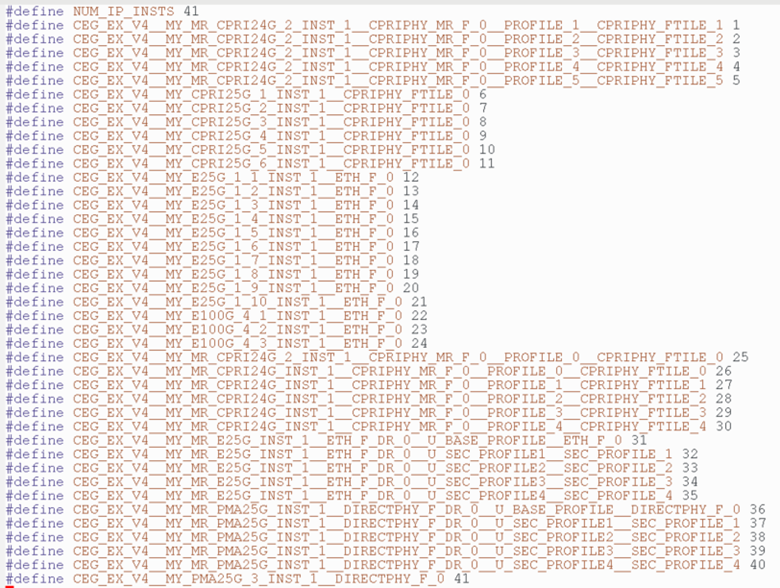

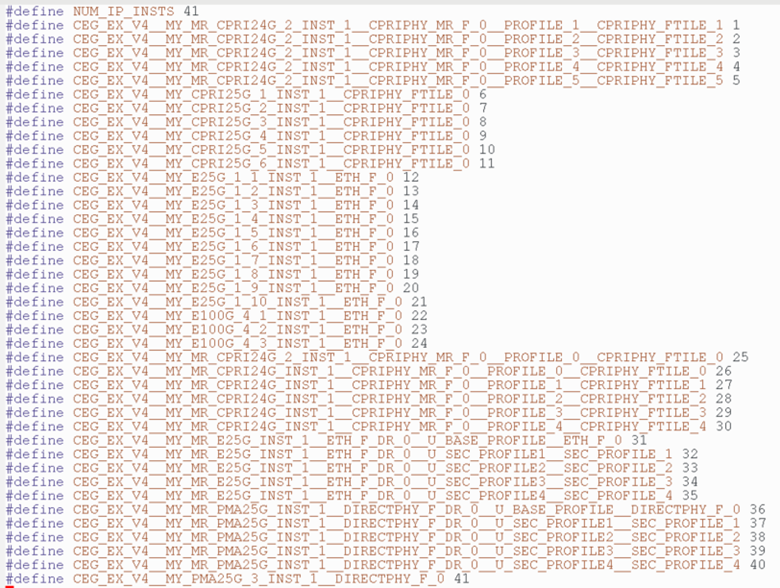

In designs with multiple dynamic reconfiguration profiles but no reconfiguration IDs specified in the QSF file, you can inspect the .h header file located in the <project directory>/support_logic directory to determine the number for each profile. The filename convention is <design name>__ip_insts_<tile location>.h

Figure 22. Header File ExampleThis figure shows an example of the header file which contains multiple instances of the F-Tile Dynamic Reconfiguration Suite . Note that the profiles shown in this figure are unrelated to the example described in section: Example: Dynamic Reconfiguration Programming Sequence.

In the above example, you can observe that the design contains 41 individual profiles which are distributed across multiple instances of IPs. Also, you can determine that the Quartus® Prime Pro Edition software has assigned profile 1 to the IP Instance whose hierarchy is shown as:

CEG_EX_V4__MY_MR_CPRI24G_2_INST_1__CPRIPHY_MR_F_0__PROFILE_1__CPRIPHY_FTILE_1

If you want to dynamically reconfigure this IP instance with this profile, you can program the Next Profile 1 register with a 15’h1 in the programming sequence as described in section: Example: Dynamic Reconfiguration Programming Sequence.

Tip: If you need to maintain awareness of the currently loaded profile in all your protocol IPs that match these actual profile assignments, you should write the current active profile numbers to scratchpad registers in your design since the Dynamic Reconfiguration Suite IP does not keep a record of all active profiles. This is helpful if your application needs to know which profiles are active at any given time.